回归

多线程

适配器模式

defer

python 笔记

科技

ROS

反射型XSS

熵

Debezium报错处理系列

pdf

DASCTF2022十月挑战赛

insert into

激光测距传感器

人手检测

camera

信奥

cocos2d

数字化转型

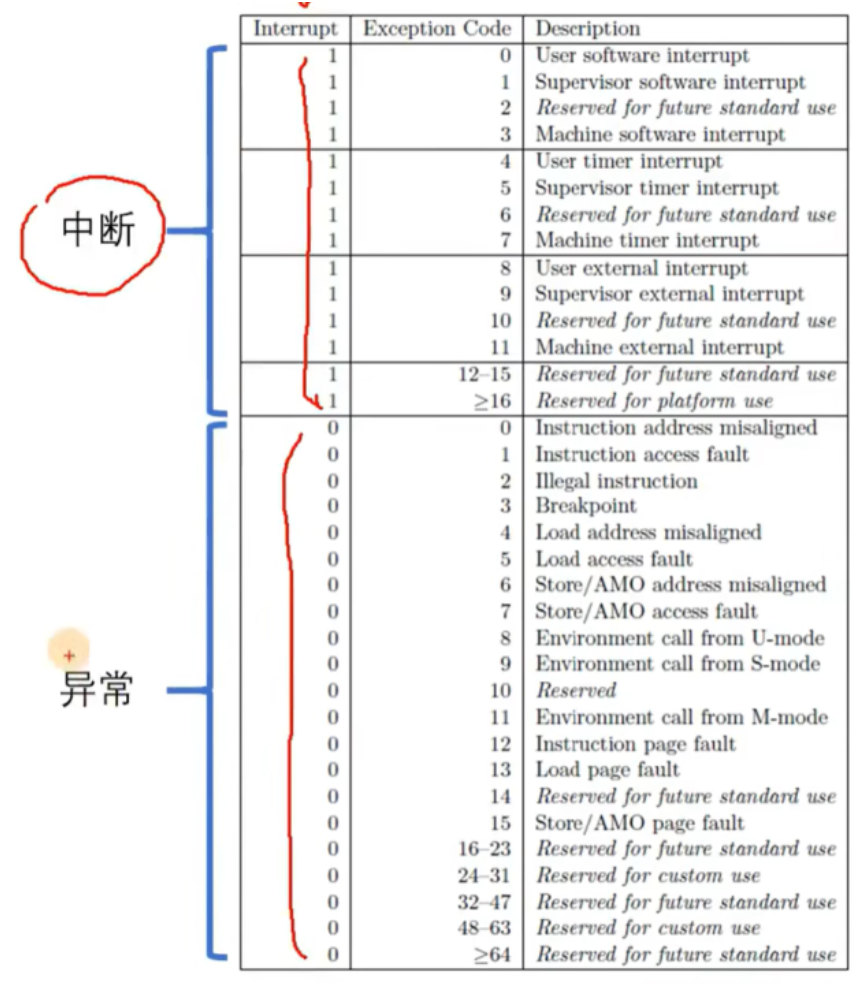

中断

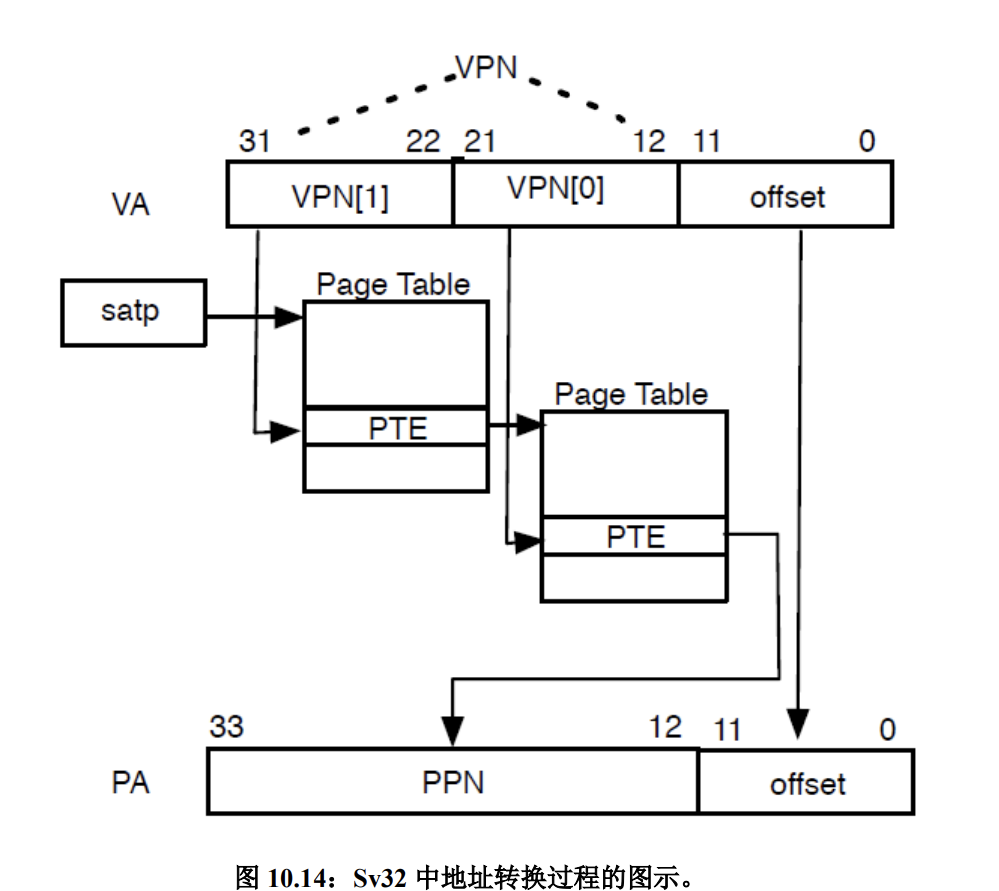

risc-v

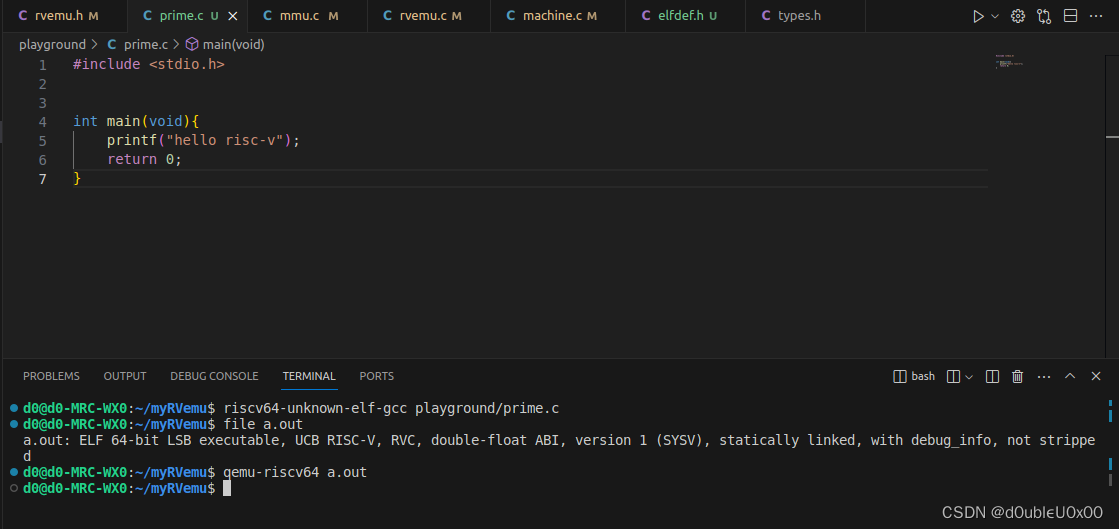

2024/4/11 16:52:16RISC-V 开发工具链的使用

原文出处:https://github.com/riscv/riscv-toolchain-conventions/blob/master/README.mkd

RISC-V Toolchain Conventions

Copyright and license information

This document is authored by:

Alex Bradbury asblowrisc.org.

Licensed under the Creative Comm…

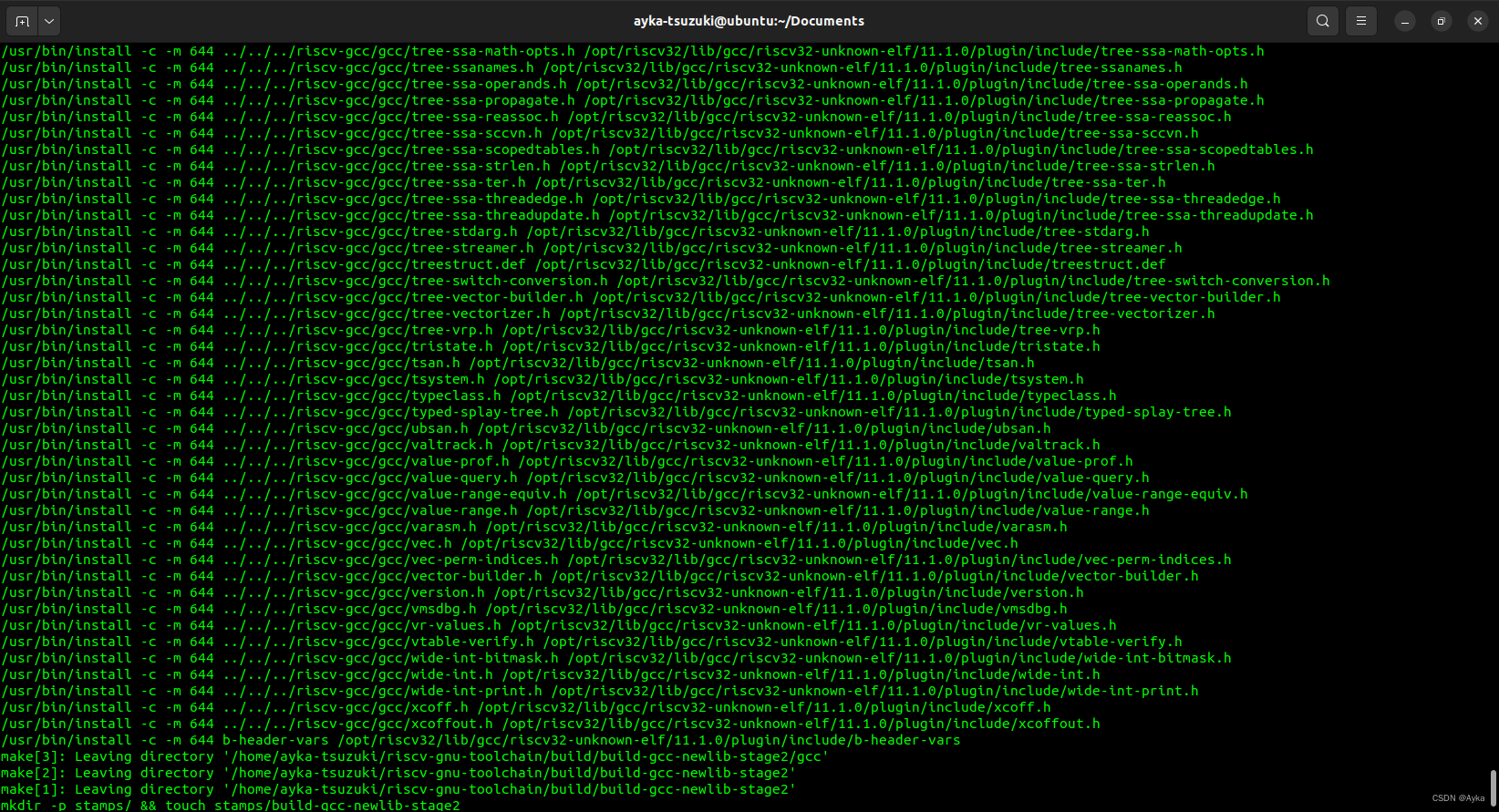

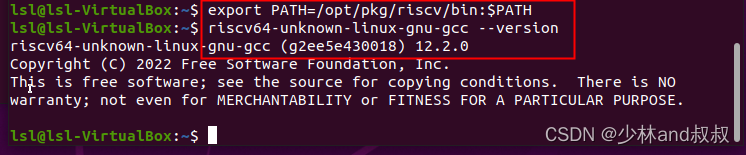

11 Ubuntu | 省时省事| riscv-gnu-toolchain工具链安装|无需编译

文章目录 序言下载预编译包解压缩,观察该包添加环境变量验证安装成功 序言

大家好我是CSDN不知名放弃领域创作者早上真好,最近想放弃学习RISC-V了,所以首先得入门。 入门RISC-V,当然需要安装RISCV的工具链,目前大多数…

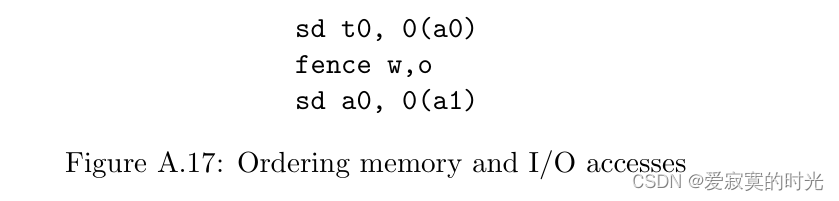

RISC-V RVWMO 内存模型解释

RISC-V RVWMO 内存模型解释

引言

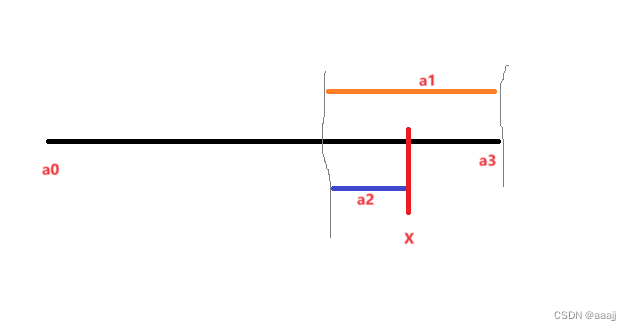

本文介绍 RISC-V RVWMO 内存模型。RVWMO 内存模型定义了什么样的全局内存顺序才是合法的。本引言部分将解释为什么会出现不合法的全局内存顺序,以及为什么需要内存模型。

首先引起乱序的全局内存顺序(指令重排序&…

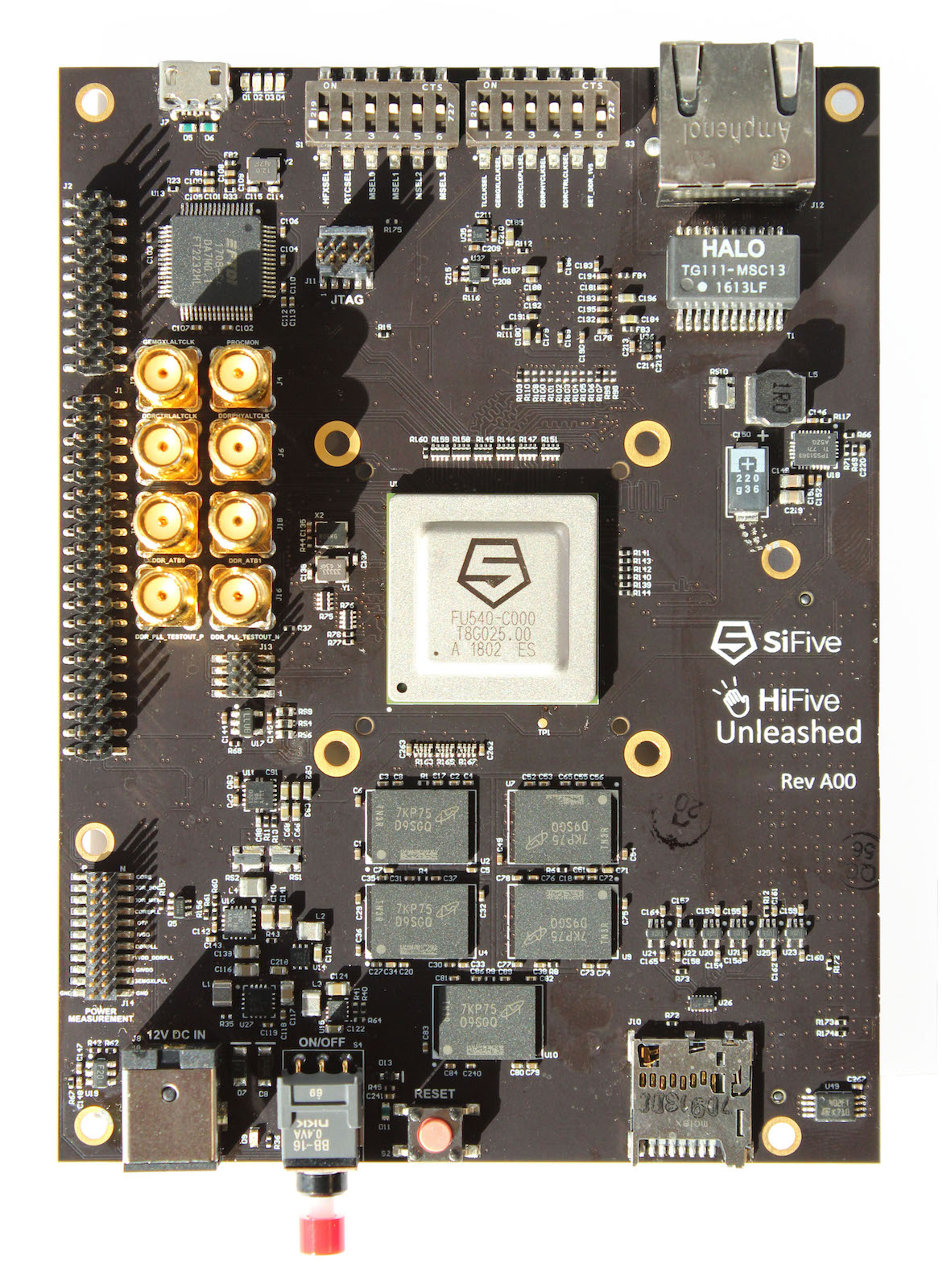

RISC-V Linux系统kernel制作

文章目录 1、下载2、编译 1、下载

Linux 官网地址:https://www.kernel.org

$ wget https://cdn.kernel.org/pub/linux/kernel/v5.x/linux-5.10.181.tar.xz

$ tar xvf linux-5.10.181.tar.xz

$ cd linux-5.10.1812、编译

安装依赖

$ sudo apt-get install -y flex bison bui…

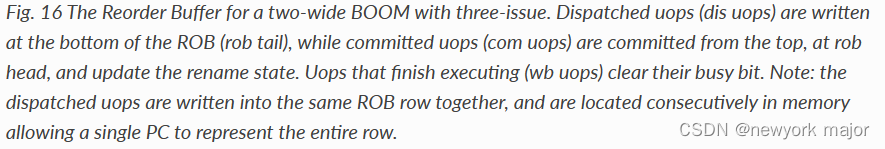

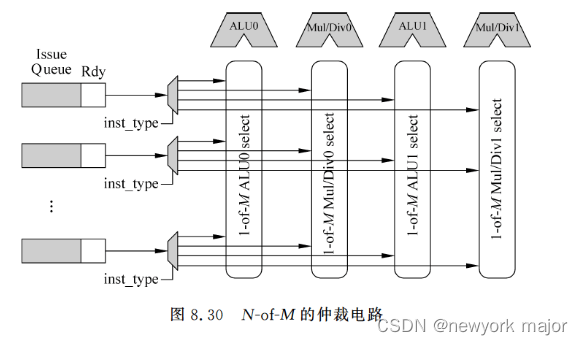

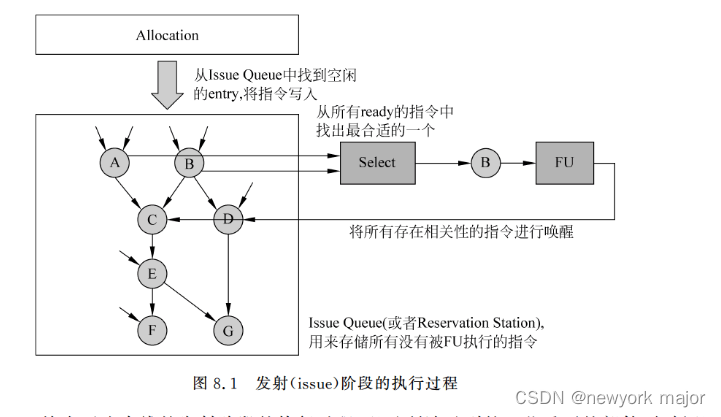

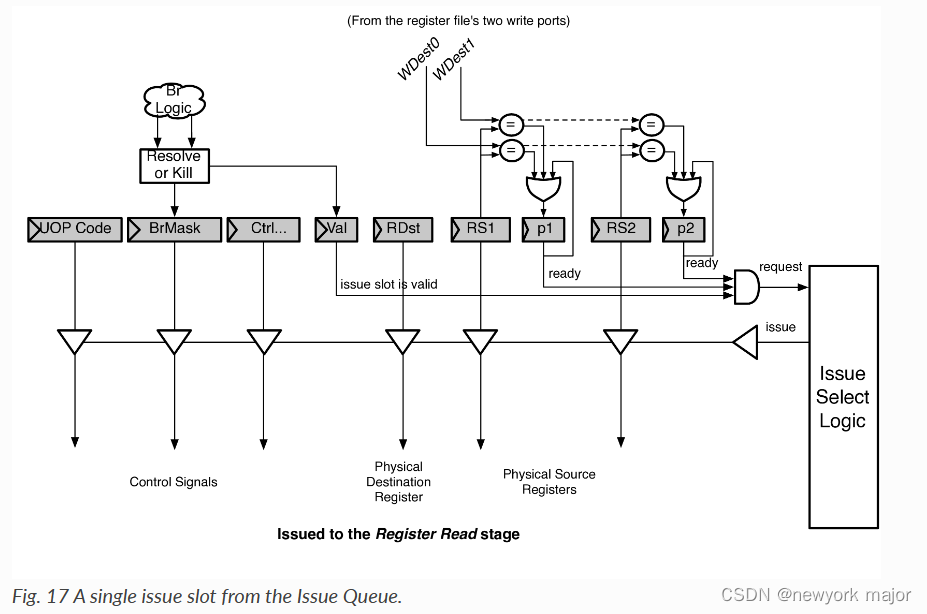

issue阶段的选择电路的实现

1-of-M的仲裁电路 为什么要实现oldest-first 功能的仲裁呢? 这是考虑到越是旧的指令,和它存在相关性的指令也就越多,因此优先执行最旧的指令,则可以唤醒更多的指令,能够有效地提高处理器执行指令的并行度,而且最旧的指…

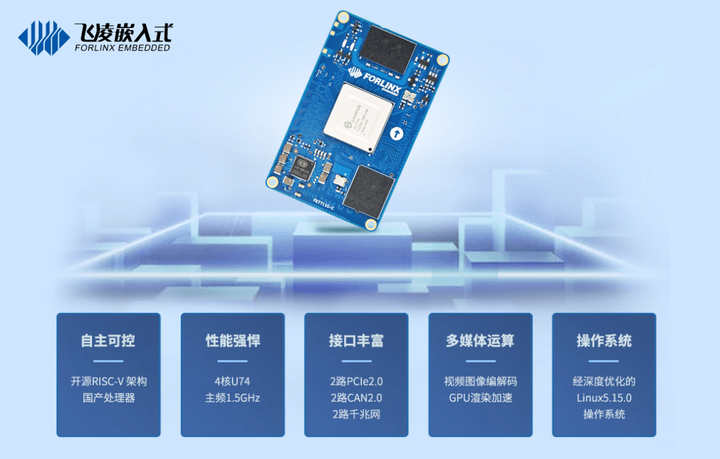

飞凌嵌入式受邀参加「RISC-V芯片应用交流会」并发表主题演讲

8月23日下午,在第三届RISC-V中国峰会现场,由赛昉科技主办的「RISC-V芯片应用交流会」吸引了诸多行业伙伴和专家到场参与。此次会议旨在分享赛昉科技高性能RISC-V芯片的软件生态、应用产品、解决方案等全面进展,共同探讨RISC-V芯片的未来发展和…

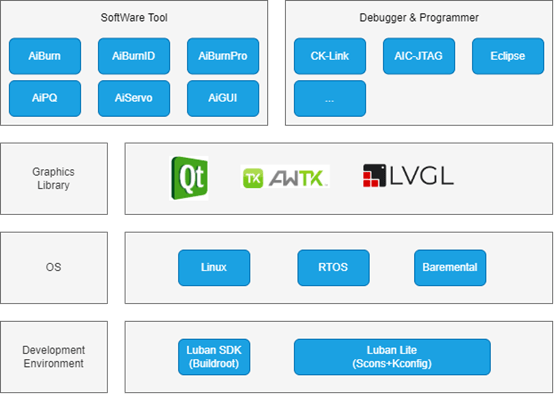

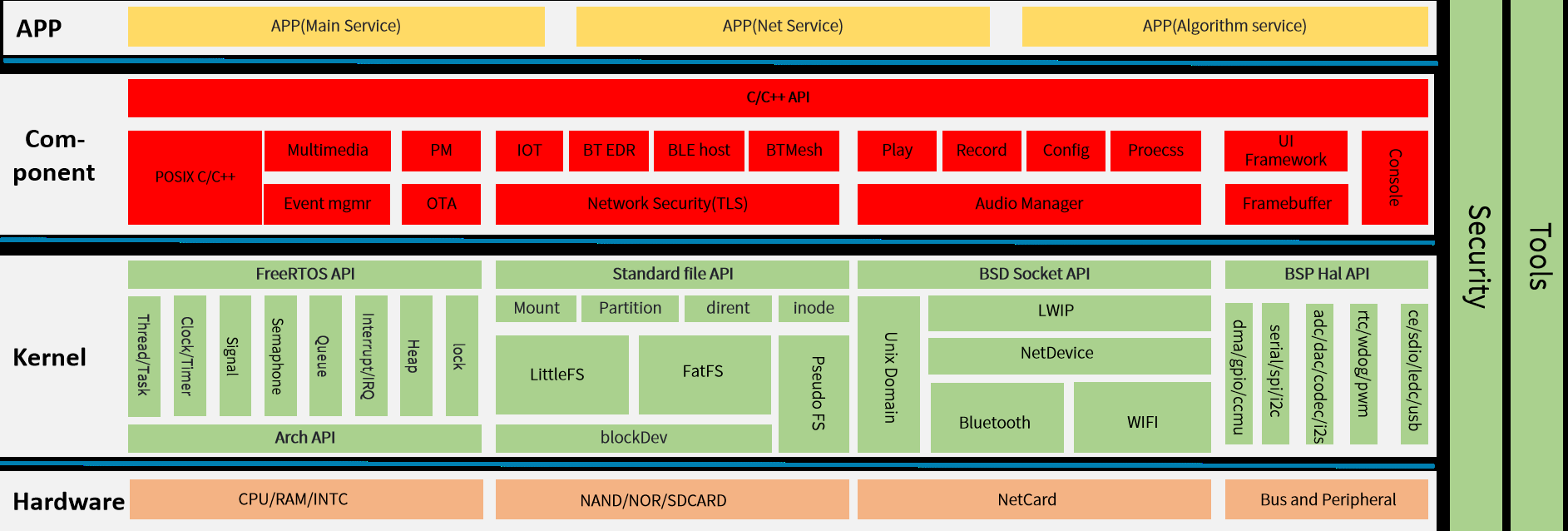

RISC-V工业级芯片公司匠芯创,宣布软件开发包SDK正式开源

近日,RISC-V芯片公司匠芯创宣布开源D21x系列工业级应用芯片软硬件开发包SDK。软件开发包涵盖了D21x开源代码、软件API库、开发手册文档、相关调试及烧录工具,并且提供多媒体中间件等多个SDK用例和应用 Demo示例,帮助企业和个人开发者快速上手…

Linux 中的 cp 命令及示例

cp代表副本。该命令用于复制文件或文件组或目录。它使用不同的文件名在磁盘上创建文件的精确映像。cp命令的参数中至少需要两个文件名。

句法: cp [选项] 源目标

cp [选项] 源目录

cp [选项] Source-1 Source-2 Source-3 Source-n 目录第一个和第二个语法用于将源文件复制到…

在WIN从零开始在QMUE上添加一块自己的开发板(一)

文章目录 一、前言二、源码编译(一)安装Msys2(二)配置GCC工具链(三)安装QEMU构建依赖(四)下载编译QEMU源码 二、QUME编程基础(一)QOM机制(二&…

RISC-V的cycle、time、instret计数器

RISC-V定义了3个64位计数器,分别为:cycle、time、instret,这三个寄存器可以用来评估硬件性能,还可以产生嘀嗒定时中断。

mingdu.zheng at gmail dot com http://blog.csdn.net/zoomdy/article/details/79443472

64位计数器

cyc…

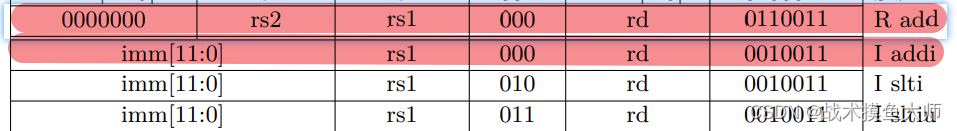

RV32执行64位的加减法及SLT/SLTU的作用

RISC-V没有条件码,如何处理32位加法溢出?如何处理32位减法借位?以及如执行64位数的加减法?

mingdu.zheng at gmail dot com https://blog.csdn.net/zoomdy/article/details/82949816

64位加法

写一段64位加法的程序:…

【risc-v】易灵思efinix FPGA riscv嵌入式软件源码分享

系列文章目录

分享一些fpga内使用riscv软核的经验,共大家参考。后续内容比较多,会做成一个系列。

本系列会覆盖以下FPGA厂商 易灵思 efinix 赛灵思 xilinx 阿尔特拉 Altera

本文内容隶属于【易灵思efinix】系列。

【risc-v】易灵思efinix FPGA sap…

rocket-chip verilator@ubuntu20.04验证环境操作指南

rocket-chip verilatorubuntu20.04验证环境操作指南 rocket-tools版本号 * (HEAD detached at 2022.12.26) ----------------------------------------------------------------------------------------------- export RISCV/home/cad/RISCV ./build.sh ./build-rv32ima.sh …

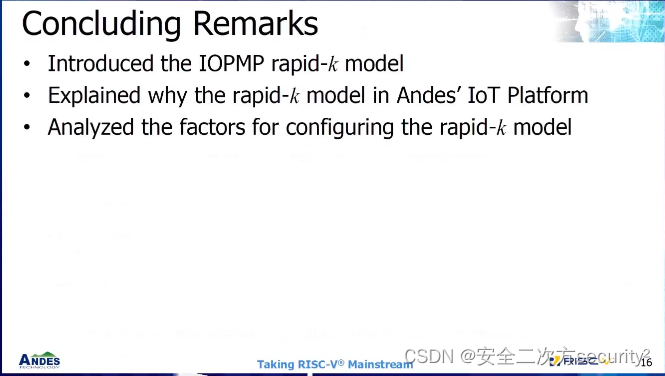

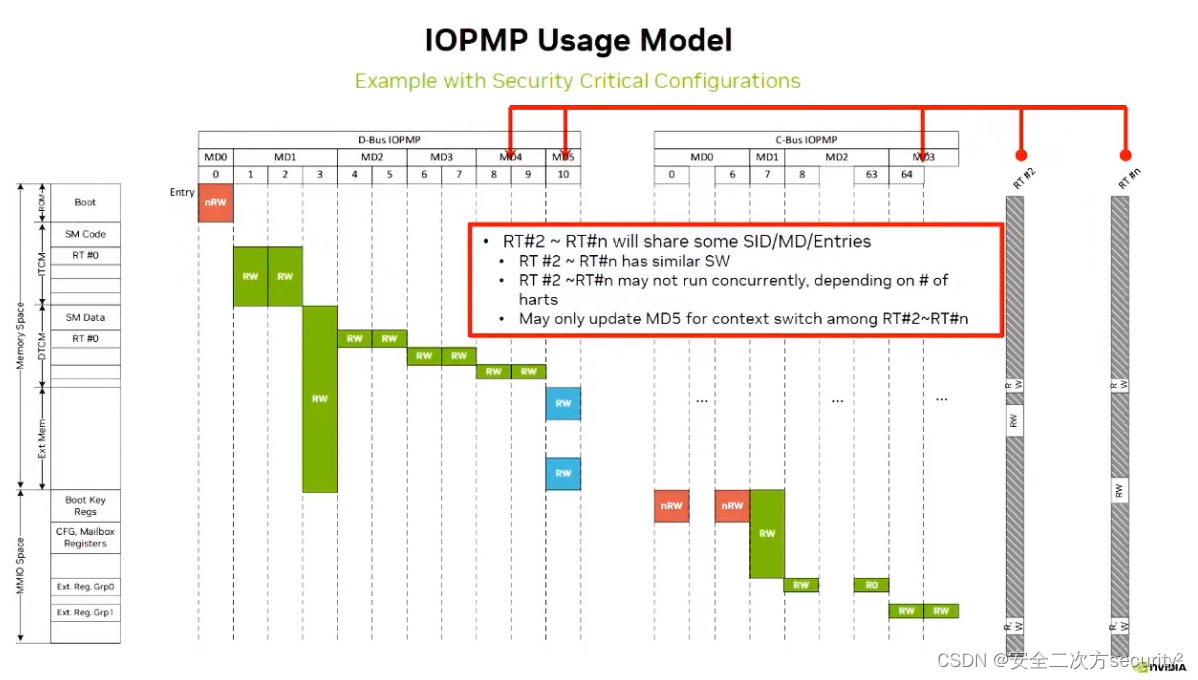

RISC-V IOPMP实际用例-Andes SoC‘s Rapid-k模型

安全之安全(security)博客目录导读

2023 RISC-V中国峰会 安全相关议题汇总 说明:本文参考RISC-V 2023中国峰会如下议题,版权归原作者所有。

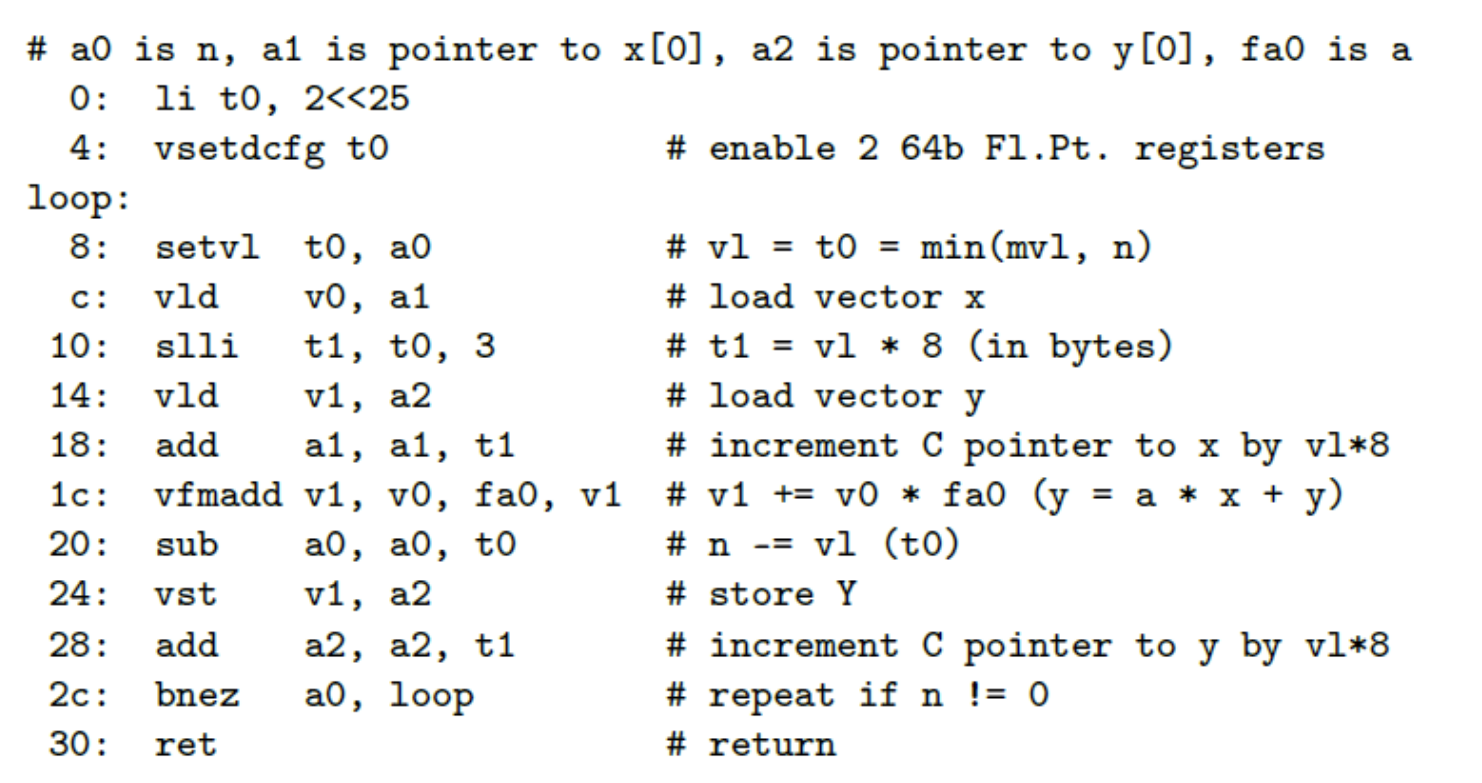

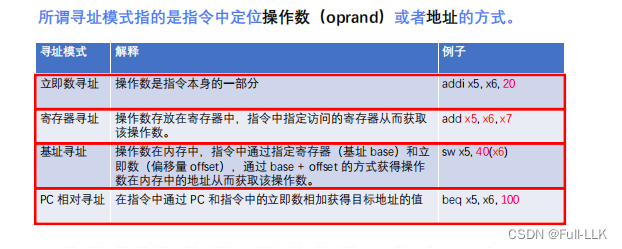

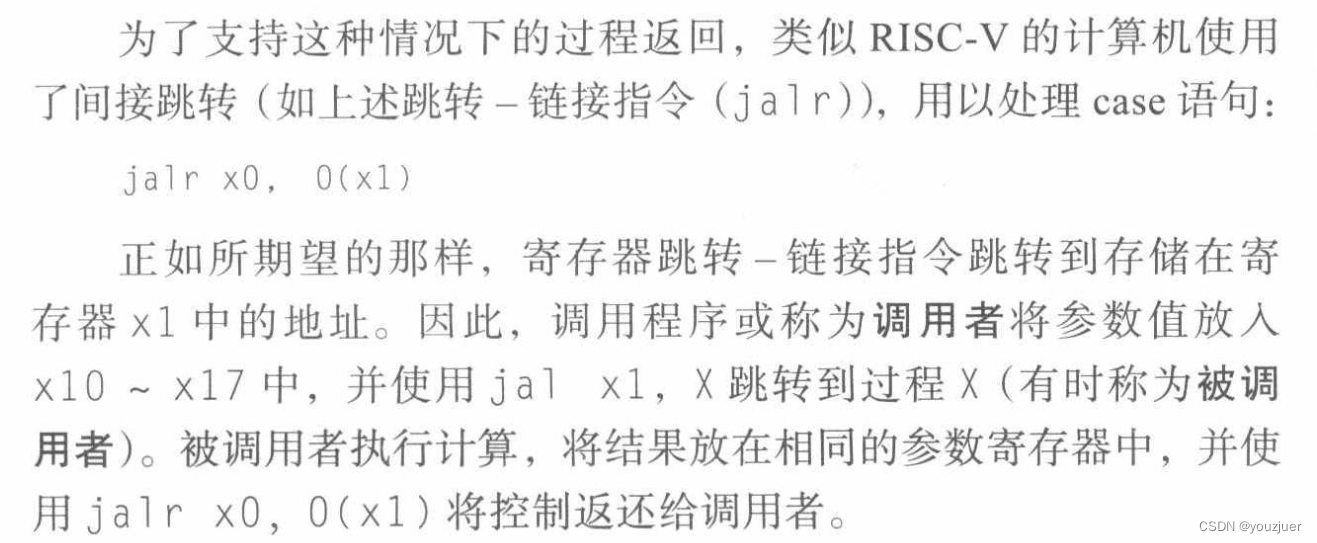

计算机组成与设计++硬件软件接口+risc-v 第二章 计算机的语言

2.3 计算机硬件的操作数 存在上述情况的根本原因是,地址是1,则存储空间8个字节,双字需要64bits,因此需要地址是64/88,所以双字的地址自增数为8

2.8 计算机硬件对过程的支持

c代码 对应的汇编代码 jalr说明ÿ…

RISC-V 基础指令汇总

加载指令 存储指令 PC寻址指令

auipc rd, imm这条指令把 imm (立即数)左移12位并带符号扩展到64位后,得到一个新的立即数,这个新的立即数是一个有符号的立即数,再加上当前 PC 值,然后存储到 rd 寄存器中。…

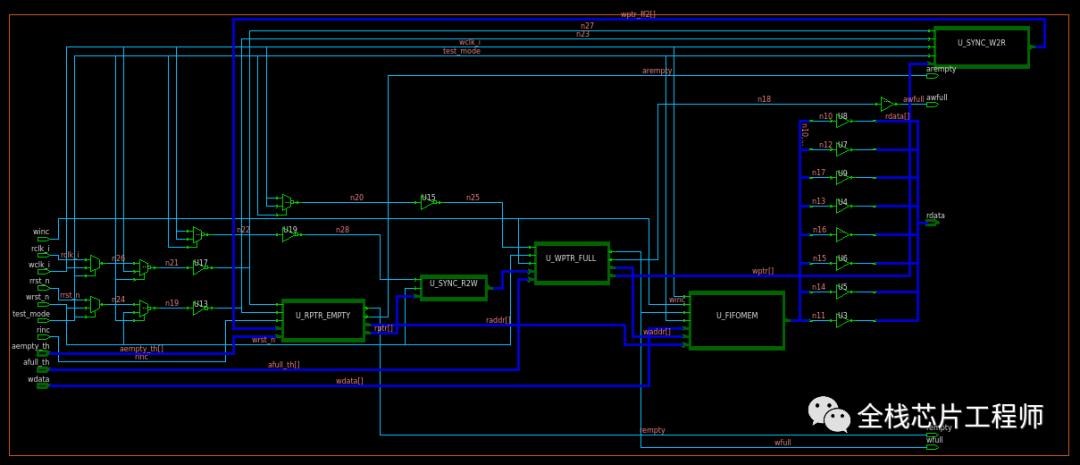

两种fifo实现方式的差异

减少数据通路翻转来降低功耗: 以FIFO (当容量较小而使用寄存器作为存储部分)设计为例,虽然理论上可以使用比较简单的数据表项逐次移位的方式,实现FIFO 的先入先出功能,但是却应该使用维护读写指针的方式(数据表项寄存器则不用移位)实现先入先出的功能。因为数据表项逐次…

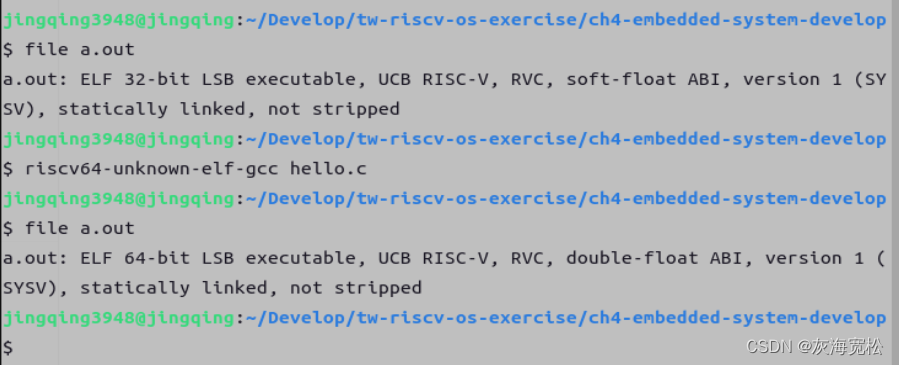

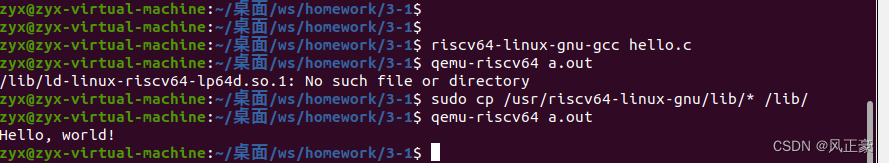

riscv64-linux-gnu-gcc编译生成32位cpu二进制

x86平台下64位设备,默认情况下编译的是elf64,比如简单的helloworld代码如下,使用readelf查看elf头部信息,格式为ELF64。

➜ cat helloworld.c

#include <stdio.h>int main()

{printf("hello!!!\n");return 0;

}…

RISC-V架构学习——C语言内嵌汇编总结

1、C语言内嵌汇编的作用 (1)优化:对于特别重要代码进行优化,出于性能的考虑; (2)C语言需要借助汇编指令来实现特殊功能。比如:C语言中访问系统寄存器就需要借助CSR指令; …

MIT 6s081 lab11:networking

lab:networking

本章实验主要是完成E1000网卡驱动程序,核心在于transmit 与 recv函数。

e1000_transmit

操作系统想要发送数据,将数据放入环形缓冲区,递增E1000_TDT,网卡会自动将数据发出。

int

e1000_transmit(st…

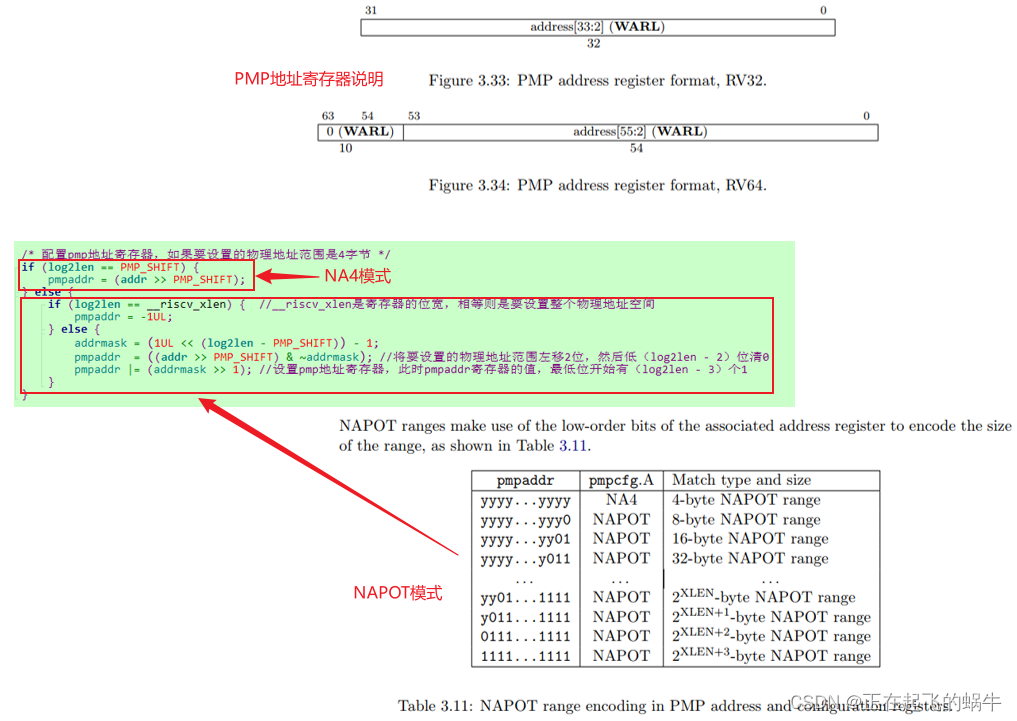

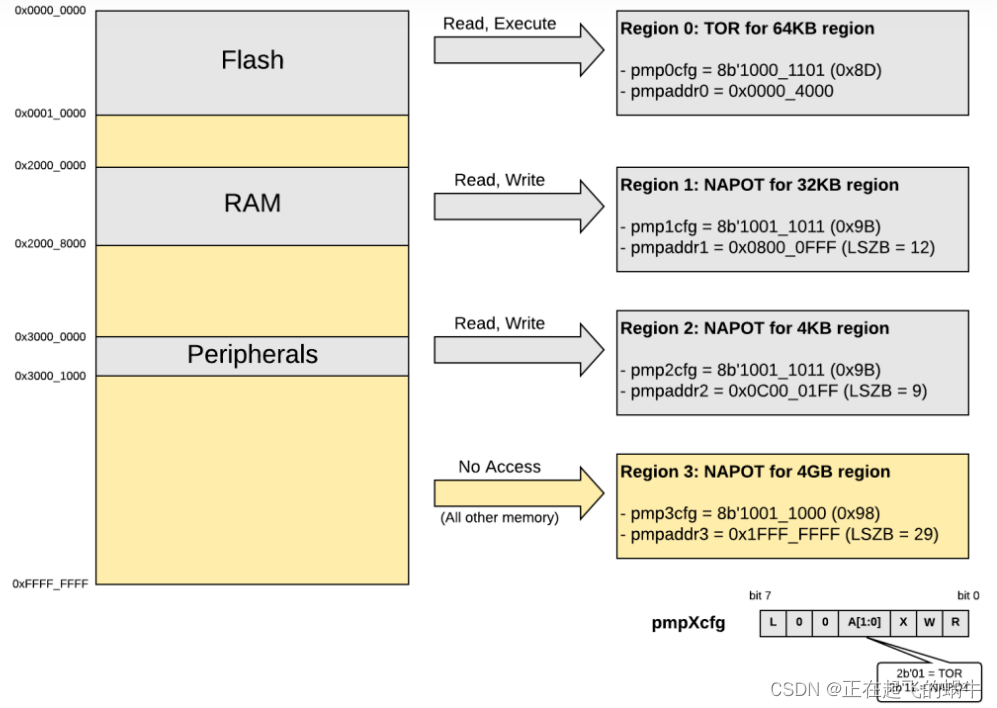

RISC-V架构——物理内存保护机制设置函数(pmp_set)解析

1、物理内存保护机制 参考博客:《RISC-V架构——物理内存属性和物理内存保护》; 2、pmp_set函数源码

int pmp_set(unsigned int n, unsigned long prot, unsigned long addr,unsigned long log2len)

{int pmpcfg_csr, pmpcfg_shift, pmpaddr_csr;unsign…

RISC-V嵌入式开发准备篇1:编译过程简介

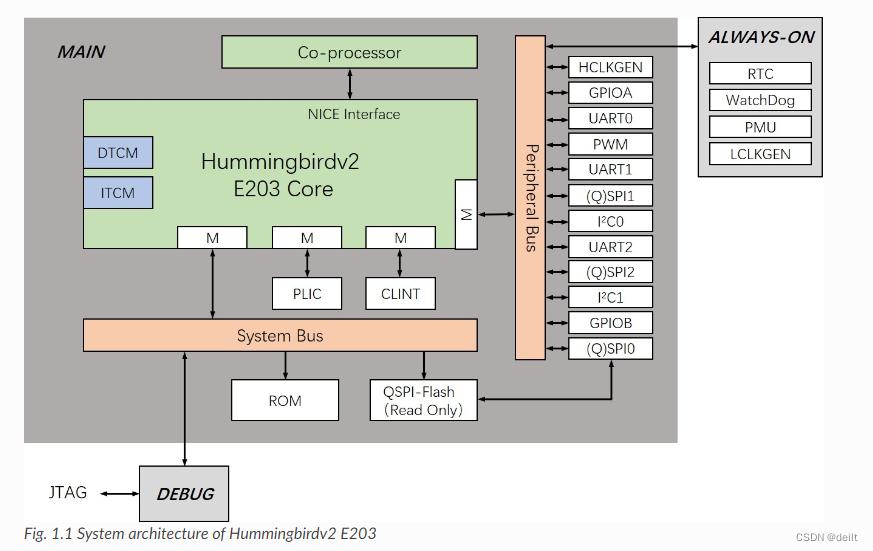

原文出处:https://mp.weixin.qq.com/s/-syKN0DibKGGPCllaeNqMg 随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》 正式上市,越来越多的爱好者开始使用开源的蜂鸟E203 RISC-V处理核,很多初学者留言询问有关RISC-V工具链使…

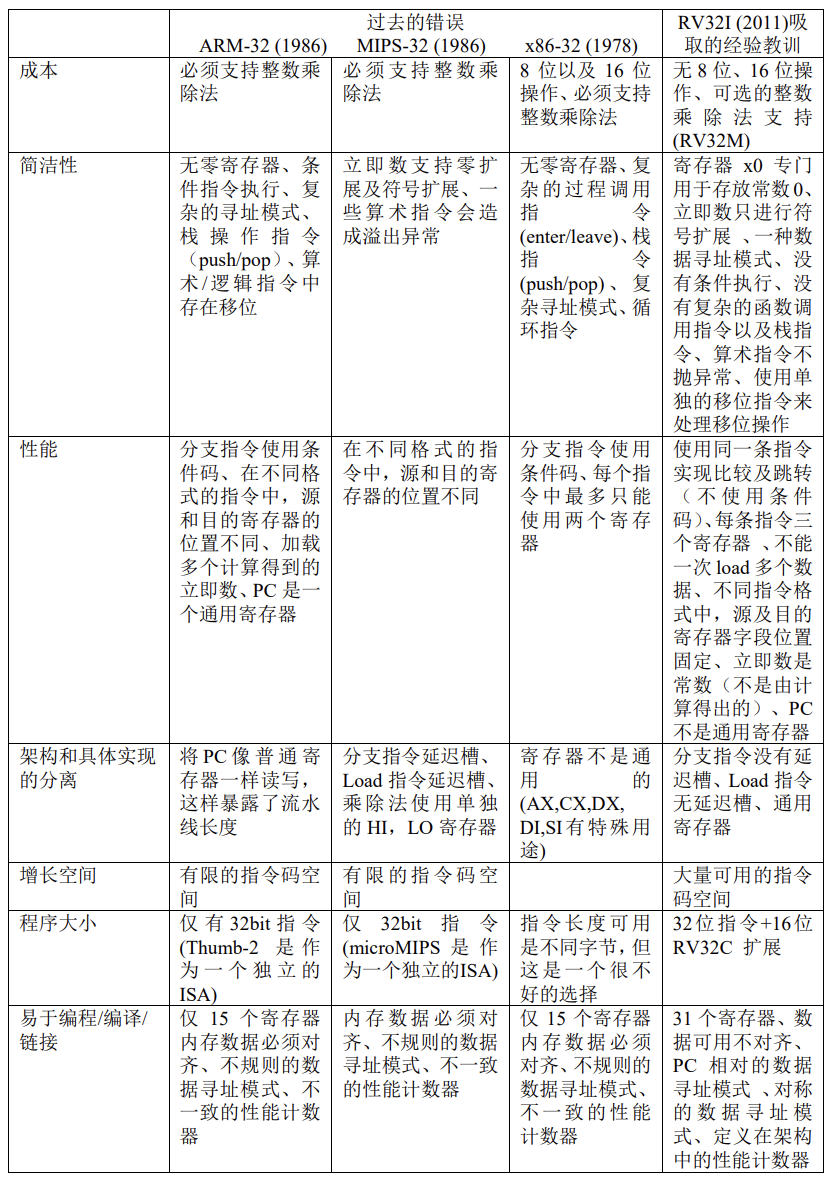

大道至简——RISC-V架构之魂(上)

本文为《RISC-V CPU设计》专栏和《RISC-V嵌入式软件开发》专栏系列文章之一。 注:本文节选自“硅农亚历山大”所著国内第一本系统介绍CPU与RISC-V设计的中文书籍《手把手教你设计CPU:RISC-V处理器篇》(预计将于2018年3~4月上市)。…

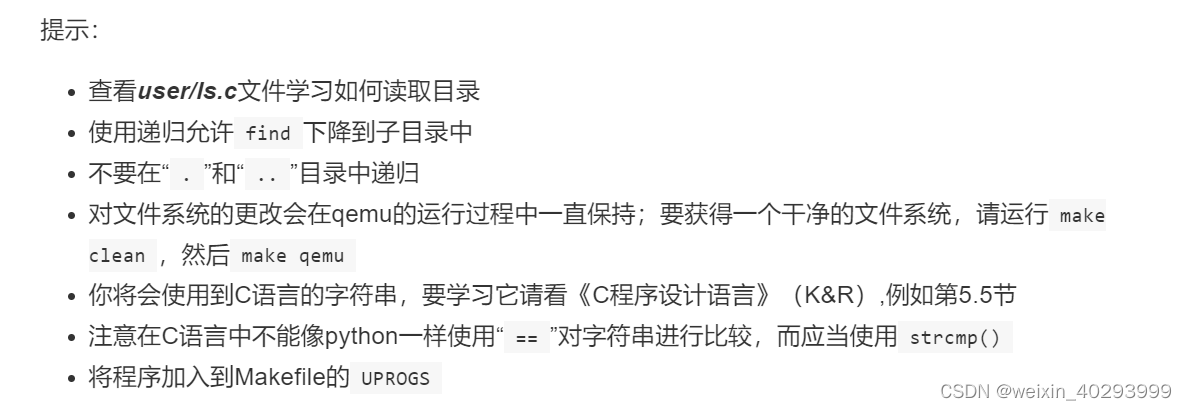

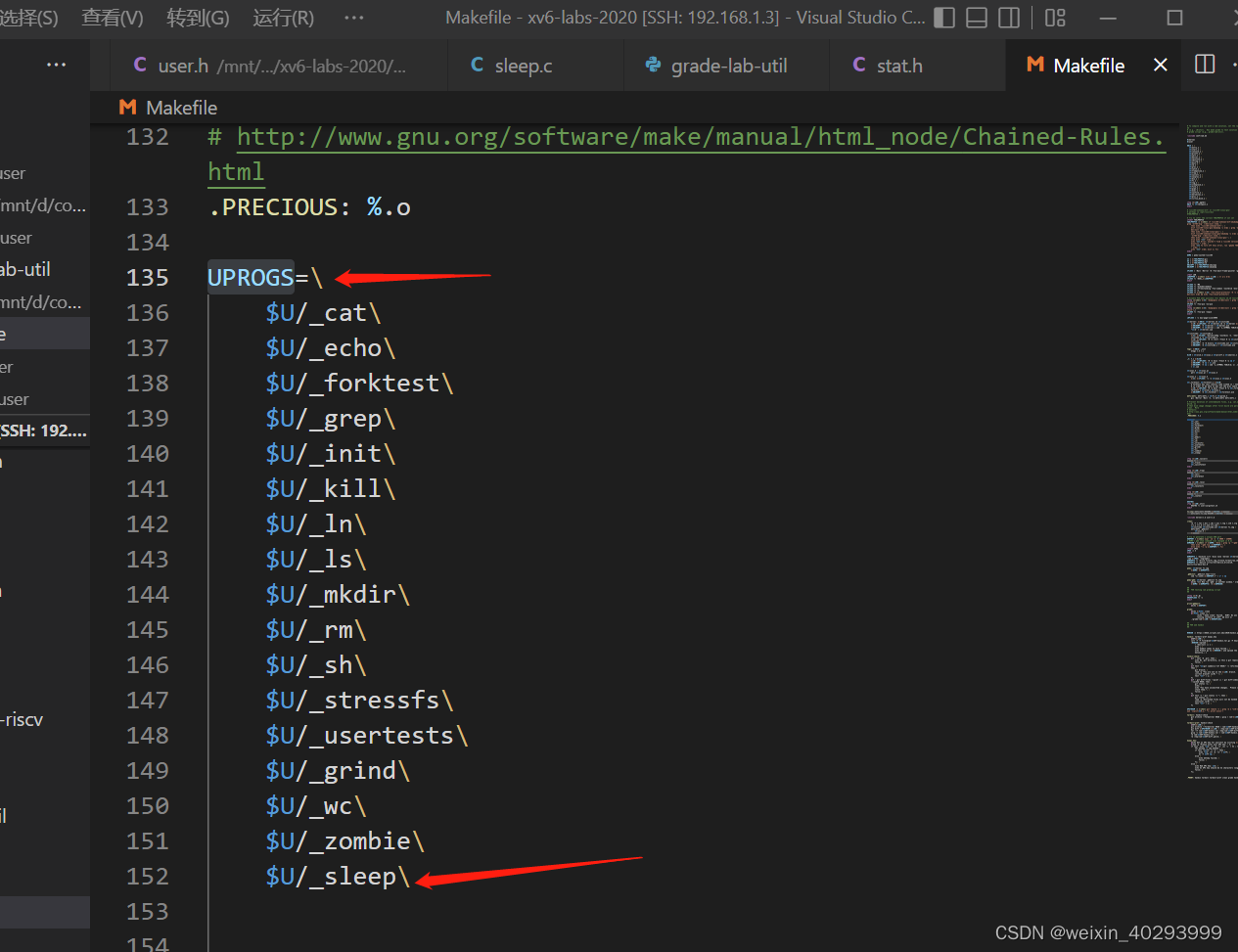

【操作系统xv6】学习记录--实验1 Lab: Xv6 and Unix utilities--未完

ref:https://pdos.csail.mit.edu/6.828/2020/xv6.html 实验:Lab: Xv6 and Unix utilities

环境搭建

实验环境搭建:https://blog.csdn.net/qq_45512097/article/details/126741793 搭建了1天,大家自求多福吧,哎。~搞环境真是折磨…

Ubuntu下运行QEMU模拟riscv64跑Debian

1.安装QEMU

下载地址:

https://www.qemu.org/download/ 建议选择稳定版本,下载后解压,然后make

wget https://download.qemu.org/qemu-8.0.3.tar.xz tar xjvf qemu-8.0.3.tar.xz cd qemu-8.0.3 ./configure --enable-kvm --enable-virtfs …

大道至简——RISC-V架构之魂(中)

本文为《RISC-V CPU设计》专栏和《RISC-V嵌入式软件开发》专栏系列文章之一。 注:本文节选自“硅农亚历山大”所著国内第一本系统介绍CPU与RISC-V设计的中文书籍《手把手教你设计CPU:RISC-V处理器篇》(预计将于2018年3~4月上市)。…

openEuler RISC-V 发行版荣获2022年中国开源创新大赛一等奖

5 月 15 日,在中央网信办信息化发展局的指导下,由中国互联网发展基金会、中国网络空间研究院、中国互联网投资基金联合主办的 “2022 年中国开源创新大赛” 正式发布了获奖名单。中国科学院软件研究所和 openEuler RISC-V SIG 联合参赛项目 “openEuler …

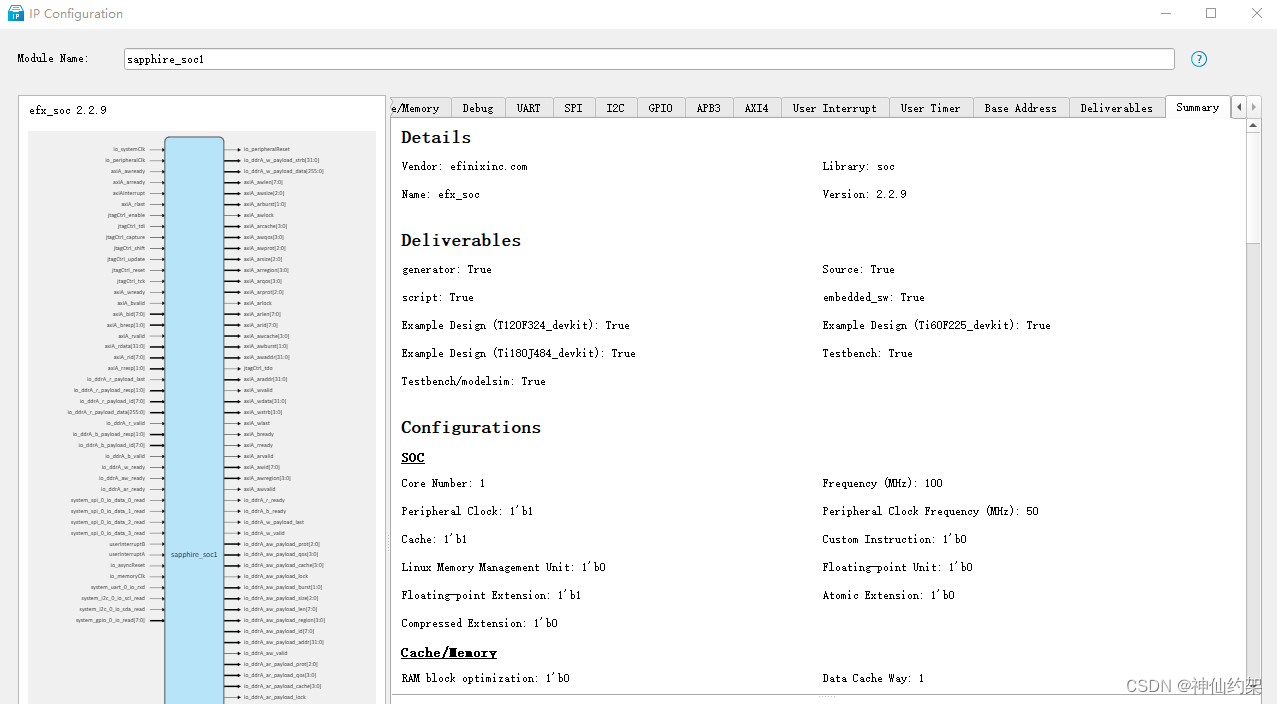

【risc-v】易灵思efinix FPGA sapphire_soc IP配置参数分享

系列文章目录

分享一些fpga内使用riscv软核的经验,共大家参考。后续内容比较多,会做成一个系列。

本系列会覆盖以下FPGA厂商 易灵思 efinix 赛灵思 xilinx 阿尔特拉 Altera

本文内容隶属于【易灵思efinix】系列。 前言 在efinix fpga中使用riscv是一…

GCC内链汇编——特定于riscv的constraints

constraints含义f浮点寄存器I12bit有符号立即数J整数0K5bit无符号立即数用于csr访问指令(如csrrwi)A一个存放在通用寄存器中的地址SA constraint that matches an absolute symbolic address.

更多特定于体系结构的constraints可见17.8.5 Constraints fo…

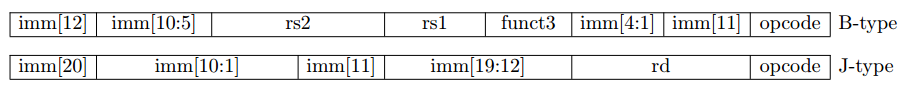

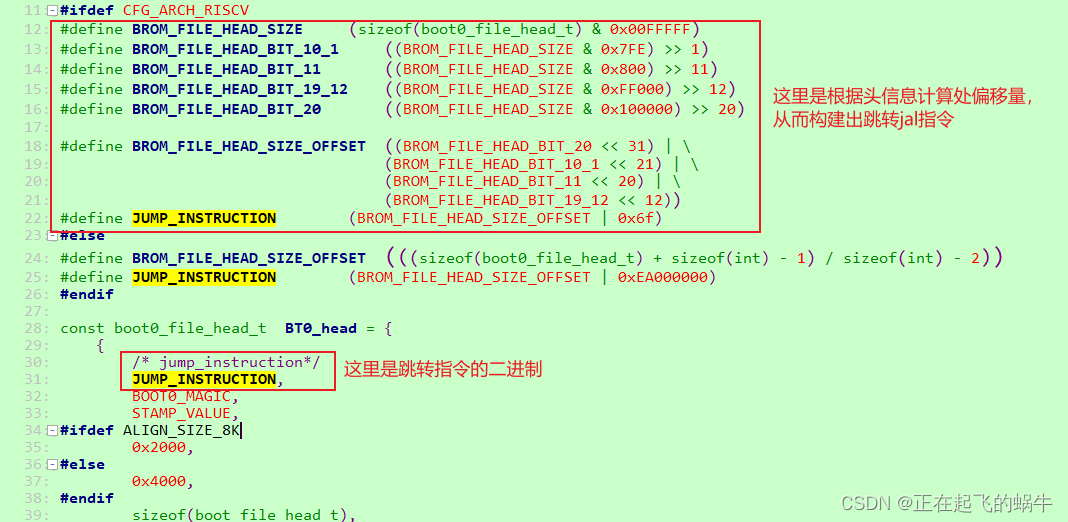

韦东山D1S板子——汇编启动代码第一行分析(.long 0x0300006f)

1、汇编启动源码 2、分析二进制:0x0300006f

2.1、反汇编代码 2.2、jal指令 jal指令的作用:跳转到当前PC值偏移offset处执行,其中offset由jal指令的bi[31:12]表示; 2.3、分析指令:j 20030 <reset>

j 20030 //伪…

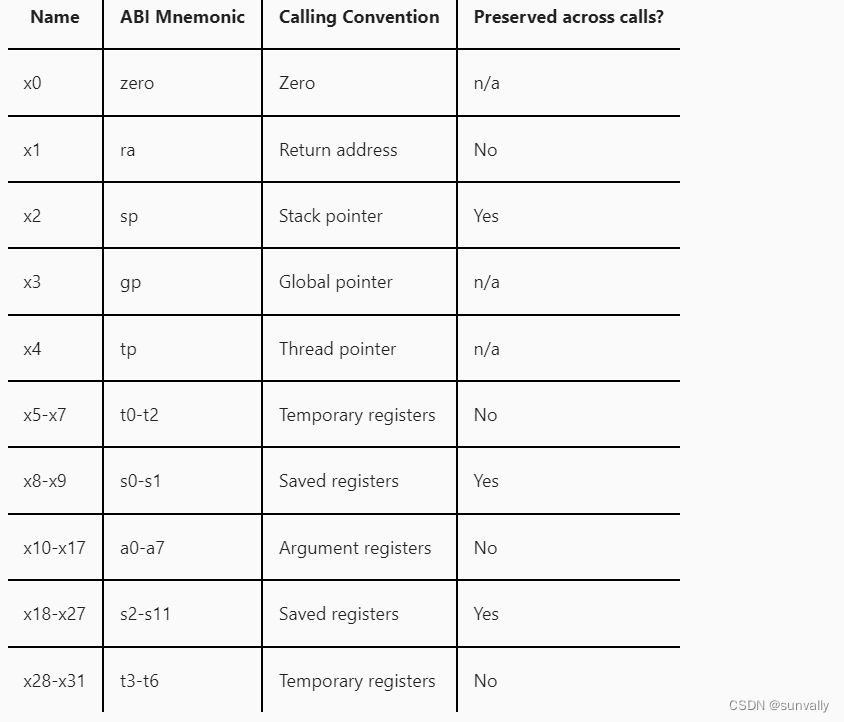

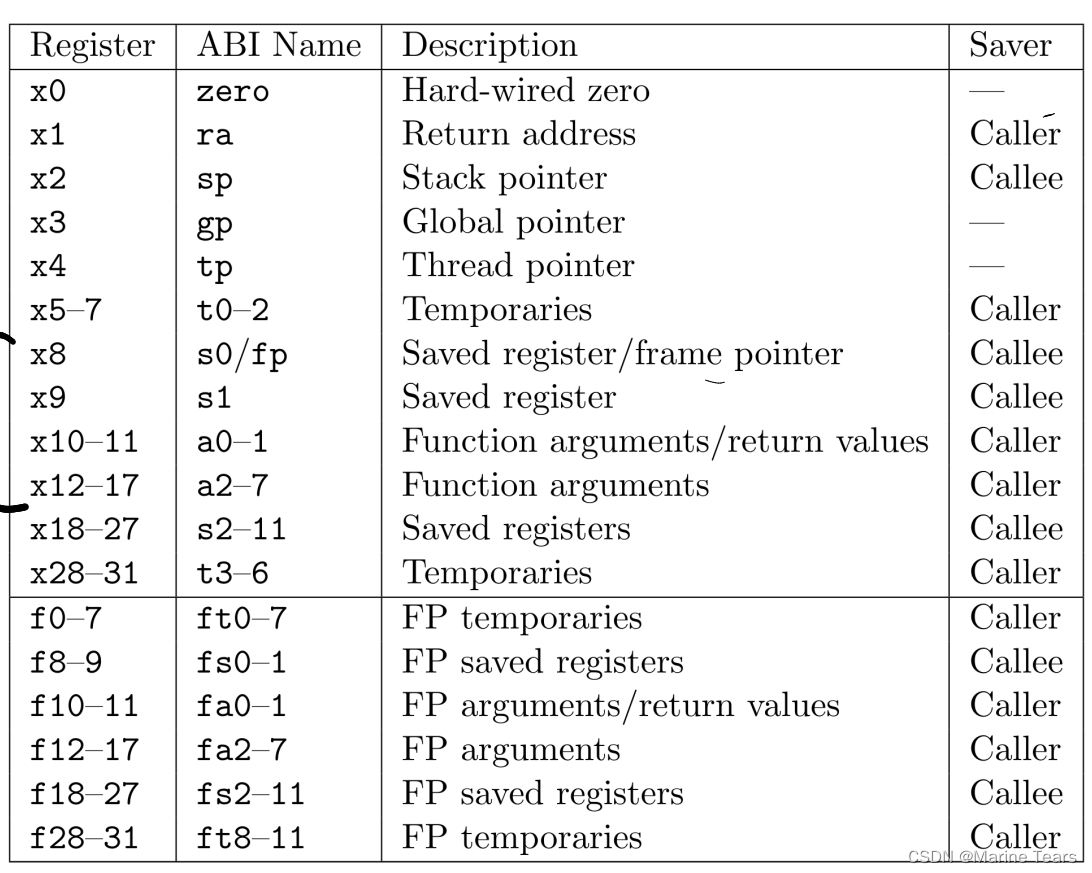

RISC-V Bytes: Caller and Callee Saved Registers

原文链接1:https://danielmangum.com/posts/risc-v-bytes-caller-callee-registers/ 原文链接2:https://zhuanlan.zhihu.com/p/77663680 //主要讲栈帧 原文链接3:https://www.jianshu.com/p/b666213cdd8a //主要讲栈帧 This is part of a new…

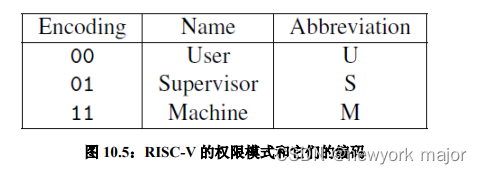

使用 C++23 从零实现 RISC-V 模拟器(6):权限支持

本节内容增加了权限表示,设置了三种权限。当 cpu 初始化时默认的权限为 Machine 模式。接下来实现这三种特权模式,随后实现 sret 和 mret 指令。

RISC-V定义了三种特权等级,分别是用户态(User Mode)、监管态ÿ…

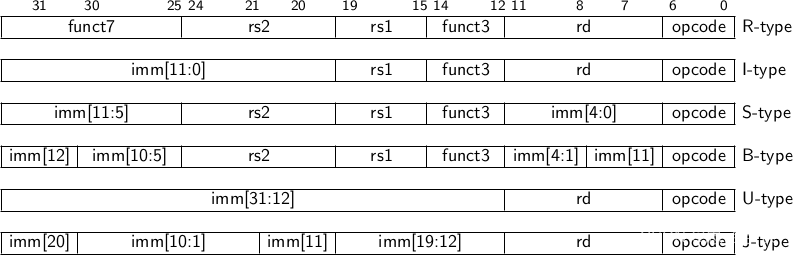

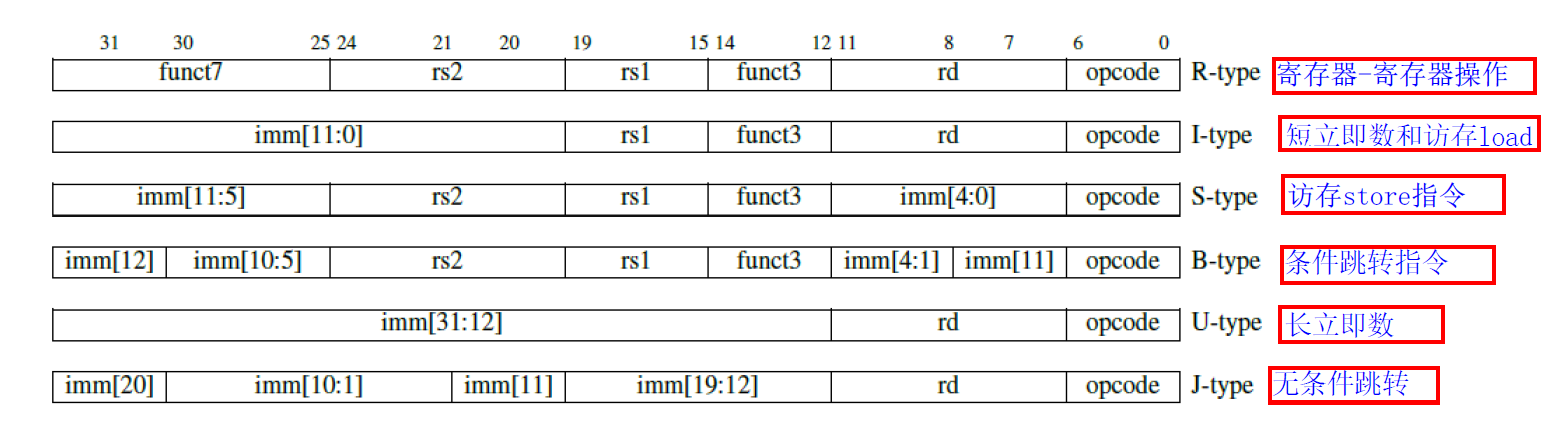

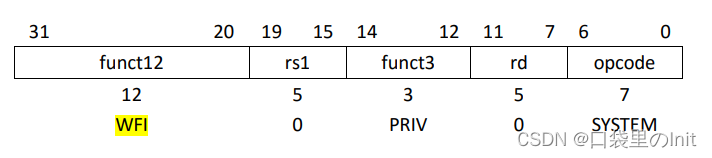

RISC-V指令格式

RISC-V指令格式 1 RISC-V指令集命名规范2 RISC-V指令集组成2.1 基础整数指令集2.2 扩展指令集 3 RISC-V指令格式3.1 指令表述3.2 指令格式 本文属于《

RISC-V指令集基础系列教程》之一,欢迎查看其它文章。 1 RISC-V指令集命名规范

前面提到过RV32I,这是…

execution unit的概念与实现----ALU

********************reading from 《超标量处理器设计》--姚永斌***************************

这是一种最普通的 FU,所有的处理器都会有这个部件,它负责对整数类型的数据进行计算,得到整数类型的结果,它一般被称做ALU(Arithmetic and Logic Unit)

整数…

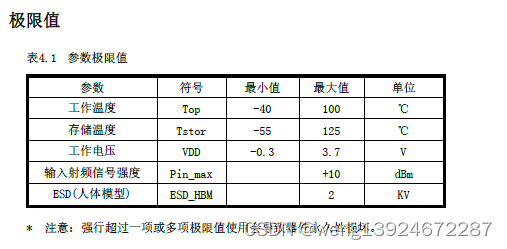

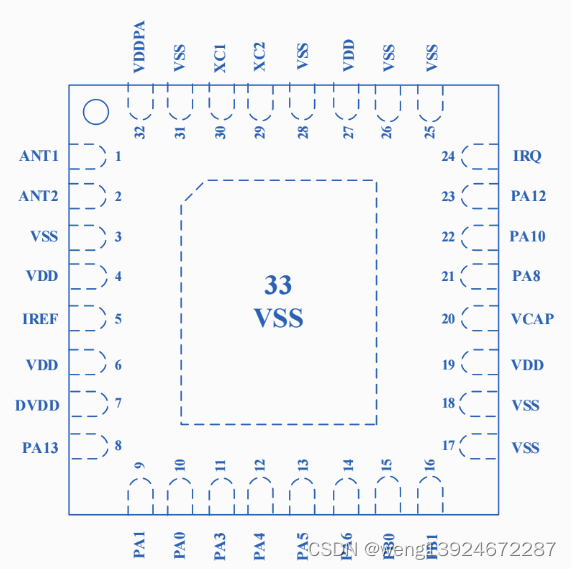

SUB-1G无线收发芯片DP4306低功耗的单片集成收发机

概述

DP4306是一款高性能低功耗的单片集成收发机,工作频率可覆盖200MHz~ 1000MHz, 芯片集成了射频接收器、射频发射器、频率综合器、GFSK调制器、GFSK 解调器等功能模块。通过SPI接口可以对输出功率、频道选择以及数据包格式进行灵活配置,并且内置CRC、…

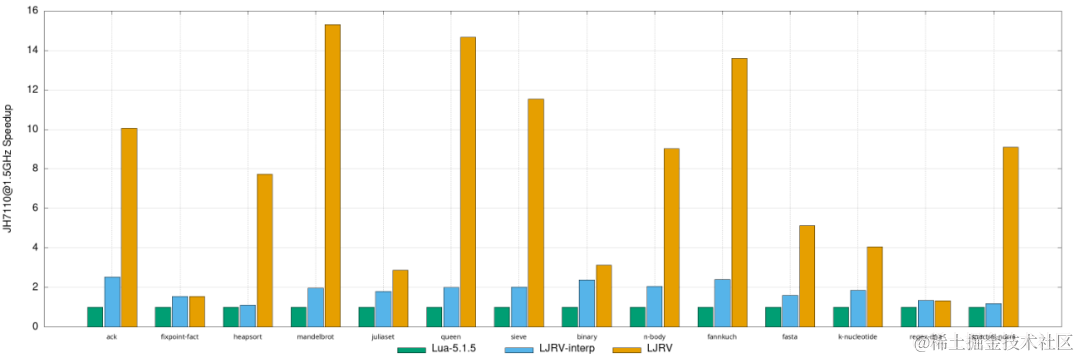

独家首发!openEuler 主线集成 LuaJIT RISC-V JIT 技术

RISC-V SIG 预期随主线发布的 openEuler 23.09 创新版本会集成 LuaJIT RISC-V 支持。本次发版将提供带有完整 LuaJIT 支持的 RISC-V 环境并带有相关软件如 openResty 等软件的支持。

随着 RISC-V SIG 主线推动工作的进展,LuaJIT 和相关软件在 RISC-V 架构下的支持也…

伪指令ret 真实指令jalr x0,x1,0

伪指令&真实指令 伪指令: 没有对应的机器码可以被汇编器翻译成一条/多条真实指令方便程序员编写/阅读代码简化常用操作 真实指令: RV32IRV32F等 ret&jalr x0,x1,0 ret: 伪指令从一个子程序返回到调用该子程序的地方 jalr x0,x1,0&…

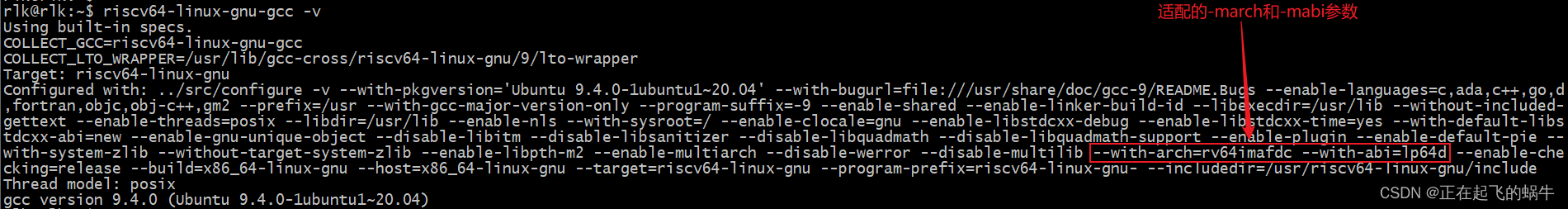

RISC-V架构常见gcc编译选项(-march、-mabi=、-mcmodel、-mlittle-endian、-mbig-endian)

1、-marchRISCV_ARCH

用于告诉编译器目标芯片的架构情况,生成对应的二进制代码比如:-marchrv32im rv32:告诉编译器生成的代码实在RISC-V架构的32位芯片上运行,就不会使用ld和sd命令,而使用lw和swim:芯片支…

RISC-V(1)——RISC-V是什么,有什么用

目录 1. RISC-V是什么

2. RISC-V指令集

3. RISC-V特权架构

4. RiscV的寄存器描述

5. 指令

5.1 算数运算—add/sub/addi/mul/div/rem 5.2 逻辑运算—and/andi/or/ori/xor/xori

5.3 位移运算—sll/slli/srl/srli/sra/srai

5.4 数据传输—lb/lh/lw/lbu/lhu/lwu/sb/sh/sw

…

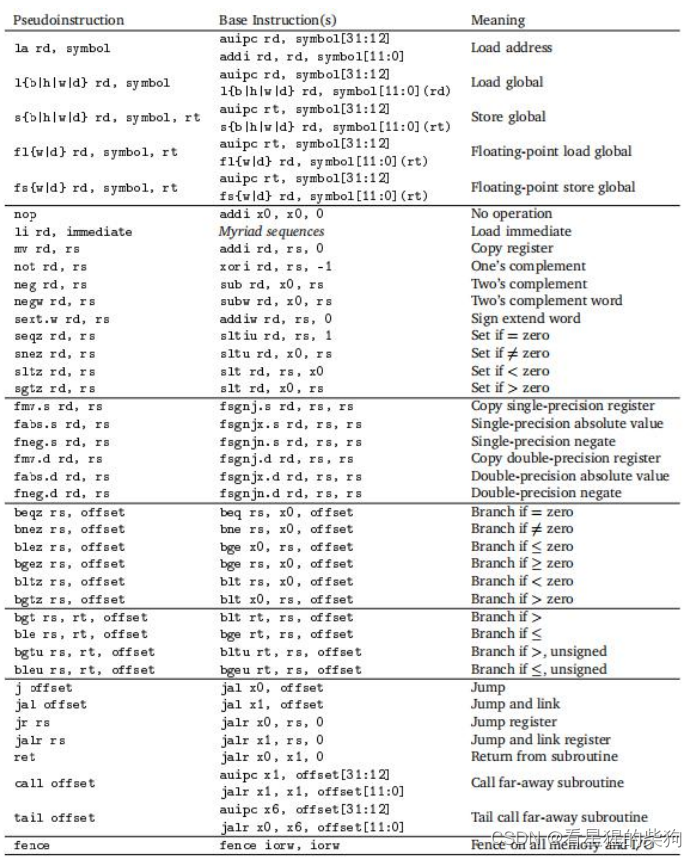

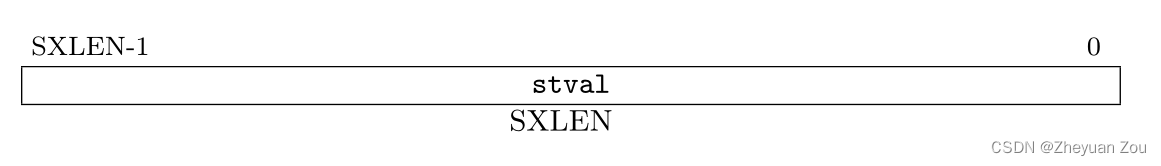

制作一个RISC-V的操作系统五-RISC-V汇编语言编程二

文章目录 RISC-V汇编指令操作对象RISC-V汇编指令编码格式小端序的概念RISC-V汇编指令分类RISC-V汇编伪指令 RISC-V汇编指令操作对象

RV32I:RISC-V32位机器整数指令集 指令集分非特权指令集和特权指令集 XLEN:变量代表当前机器的字长(32位 64…

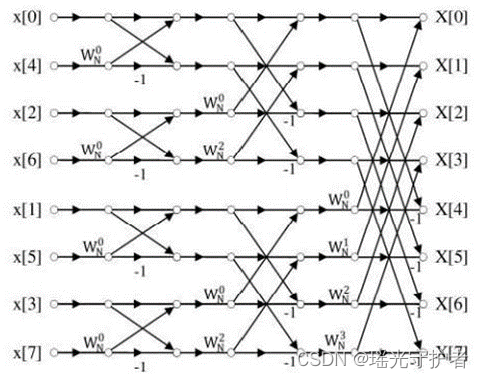

【RISC-V DSP设计】基于CEVA DSP架构的指令集分析(一)-总体介绍

目录

一、引言

二、CEVA-BX1™ DSP Library 概述

三、CEVA-BX1™ DSP Library 功能与特点

四、CEVA-BX1™ DSP Library 优势 今天开始我们继续对CEVA DSP的架构和指令集进行分析,基于对CEVA DSP的分析和了解,后续可以进行基于RISC-V内核架构的DSP指令…

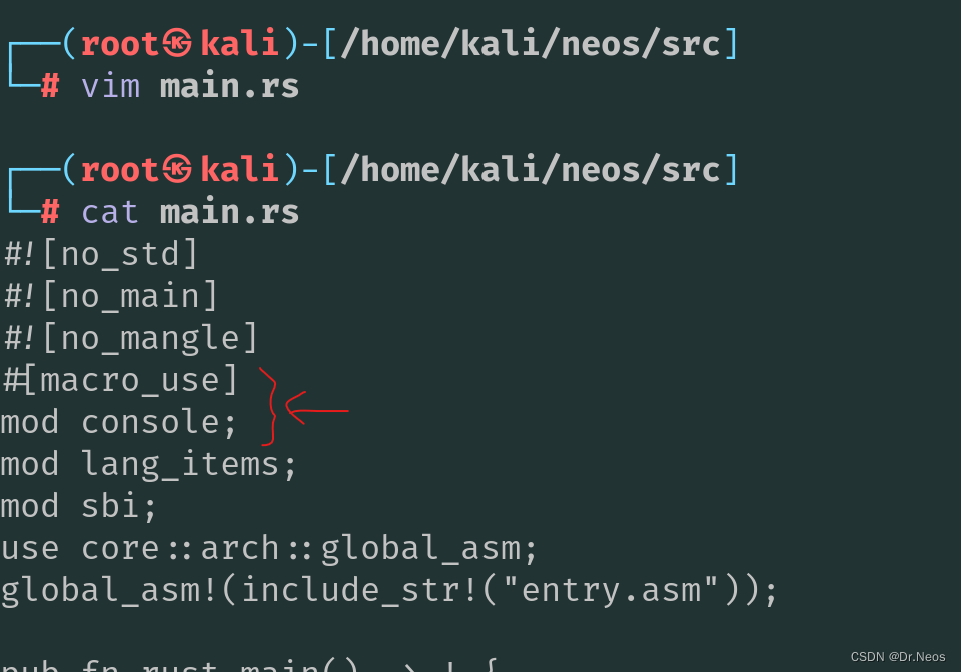

清华大学操作系统rCore实验-第一章-应用程序与基本执行环境

清华大学操作系统实验—rCore—应用程序与基本执行环境 零、前言一、创建新项目neos二、配置执行环境1、切换riscv目标平台2、移除标准库std依赖(1)切换Rust核心库-core(2)注释println!宏,暂时绕过(3&#…

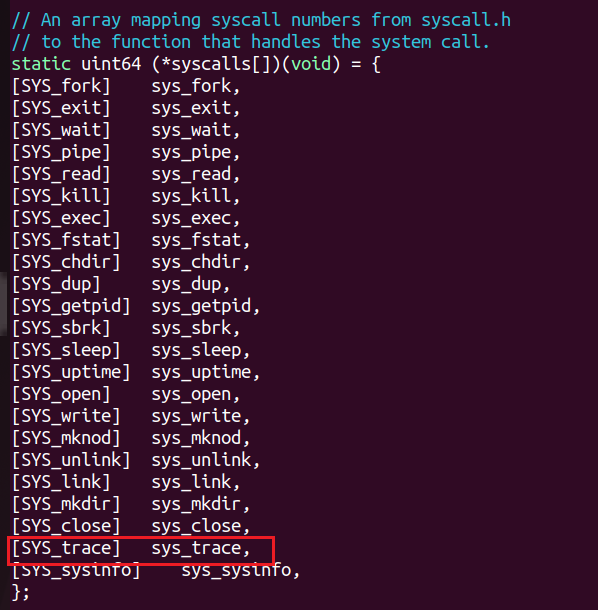

6.1810: Operating System Engineering <Lab2 syscall: System calls>

课程链接:6.1810 / Fall 2023

一、本节任务 二、要点

操作系统要满足三要素:并发、隔离、交互(multiplexing, isolation, and interaction)。

宏内核(monolithic kernel):是操作系统核心架构…

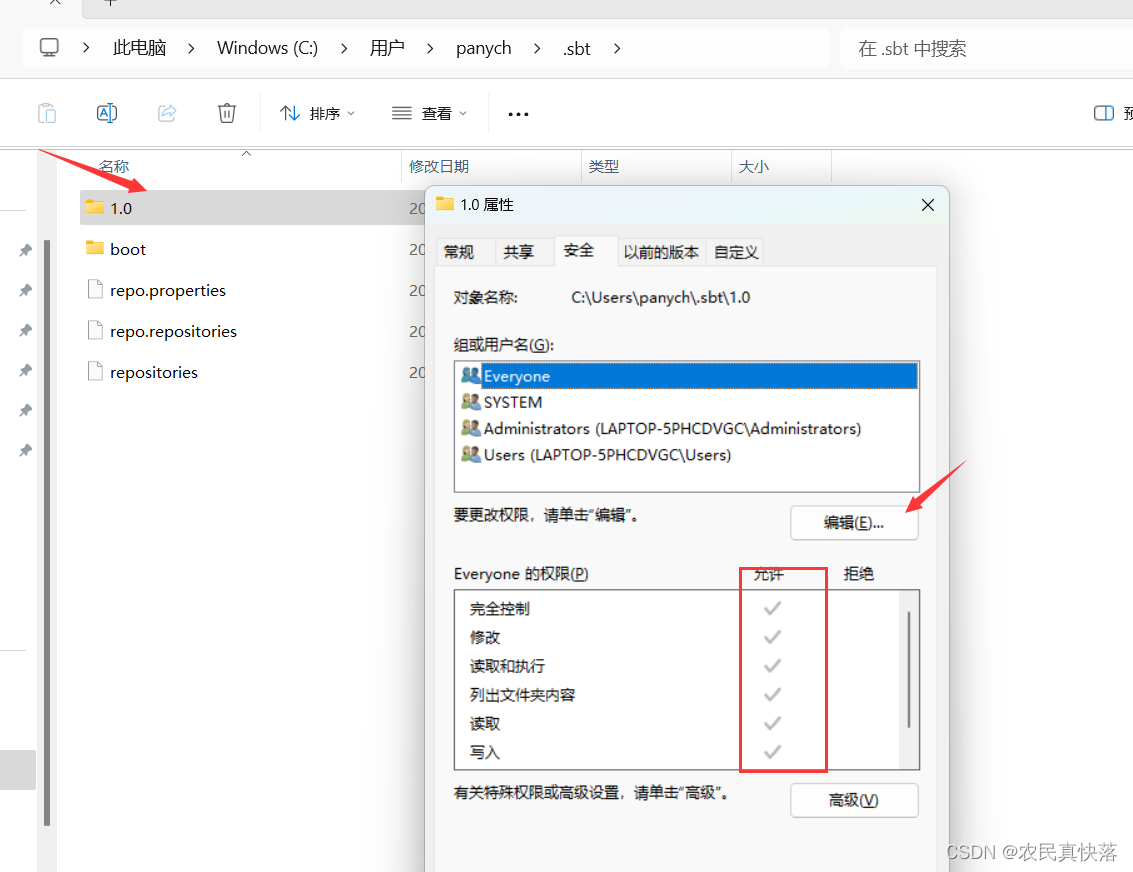

【IC设计】Windows下基于IDEA的Chisel环境安装教程(图文并茂)

Chisel环境安装教程 第一步 安装jdk,配置环境变量第二步 安装sbt,不用配置环境变量第三步 安装idea社区版第四步 离线安装scala的idea插件第五步 配置sbt换源1.切换目录2.创建repositories文件3.配置sbtconfig.txt文件 第六步 使用chisel-tutorial工程运…

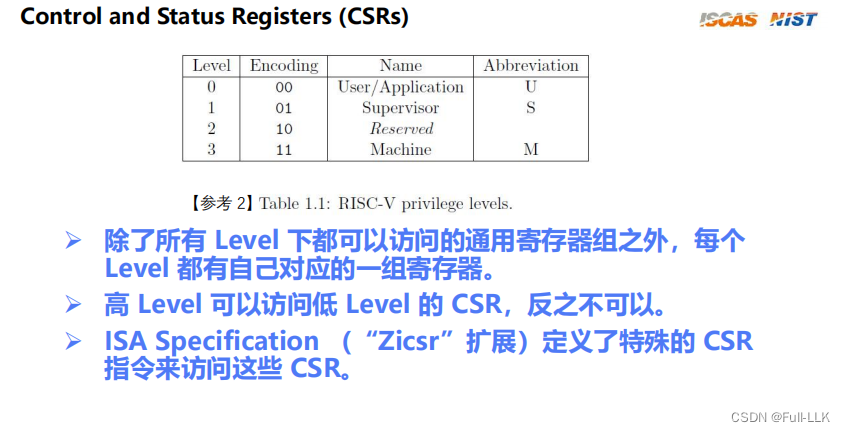

RISC-V(2)——特权级及特权指令集

目录

1. 特权级

2. 控制和状态寄存器(CSR)

2.1 分类 2.2 分析 1. 特权级 一个 RISC-V 硬件线程(hart)是运行在某个特权级上的,这个特权级被编码到一个或者多个 CSR(control and status register&a…

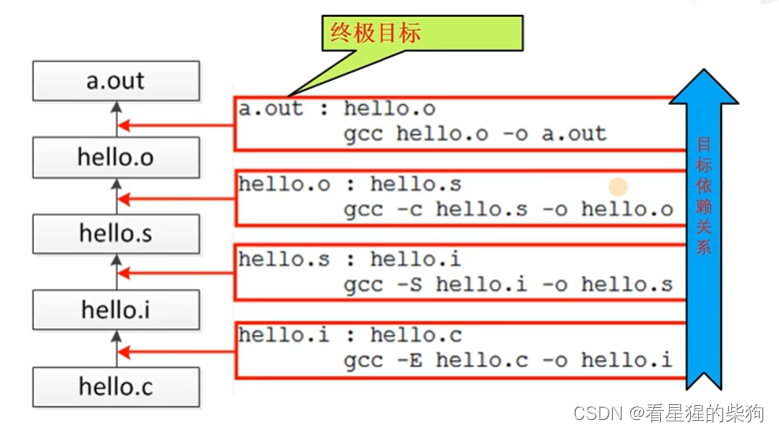

制作一个RISC-V的操作系统三-编译与链接

文章目录 GCCGCC简介GCC的命令格式gcc -Egcc -cgcc -Sgcc -ggcc -vGCC的主要执行步骤GCC涉及的文件类型针对多个源文件的处理 ELFELF介绍ELF文件格式ELF文件处理相关工具:Binutils(binary utility)readlelf -hreadelf -S或readelf -SW&#x…

RISC-V嵌入式开发准备篇2:嵌入式开发的特点介绍

原文出处:https://mp.weixin.qq.com/s/ljYZwMj3JaPN29dTAXA3bQ 随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》 正式上市,越来越多的爱好者开始使用开源的蜂鸟E203 RISC-V处理核,很多初学者留言询问有关RISC-V工具链使…

RISC-V反汇编显示原始指令和寄存器编号

反汇编时添加 -M no-aliases,numeric选项,输出原始指令和寄存器编号。

mingdu.zheng at gmail dot com https://blog.csdn.net/zoomdy/article/details/82981599

调用objdump反汇编,默认情况下,会将指令反汇编成伪指令或指令别名࿰…

RISC-V嵌入式开发入门篇2:RISC-V汇编语言程序设计(下)

原文出处:https://mp.weixin.qq.com/s/Ln4qBYvSsgRvdiK1IJqI6Q 随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》正式上市,越来越多的爱好者开始使用开源的蜂鸟E203 RISC-V处理核,很多初学者留言询问有关RISC-V工具链使…

RISC-V加载常量(立即数或地址)

RISC-V使用I-type格式的指令和U-type格式的指令加载立即数,I-type格式包含12位立即数,U-type格式包含20位立即数,而且这20位是加载到寄存器的高20位的。所以,一条I-type指令加上一条U-type指令就可以加载32位的常量,包…

RISC-V堆栈指针

RISC-V使用“full-descending”堆栈模型,堆栈寄存器用的是x2通用寄存器,要求128位对齐。

mingdu.zheng at gmail dot com http://blog.csdn.net/zoomdy/article/details/79358412

RISC-V堆栈寄存器用的是x2,这在 The RISC-V Instruction Se…

RISC-V汇编指南

原文出处:https://github.com/riscv/riscv-asm-manual/blob/master/riscv-asm.md

RISC-V Assembly Programmer’s Manual

Copyright and License Information

The RISC-V Assembly Programmer’s Manual is

© 2017 Palmer Dabbelt palmerdabbelt.com ©…

对RISC-V前途的一些看法

我是比较看好RISC-V的前途的,首先它出自大名鼎鼎的UC Berkeley;并且成立了RISC-V基金会,基金会成员中不乏高通这样的半导体公司和谷歌这样的软件公司;它采用了比较宽松的BSD授权方式,虽然其本身是开源的,但…

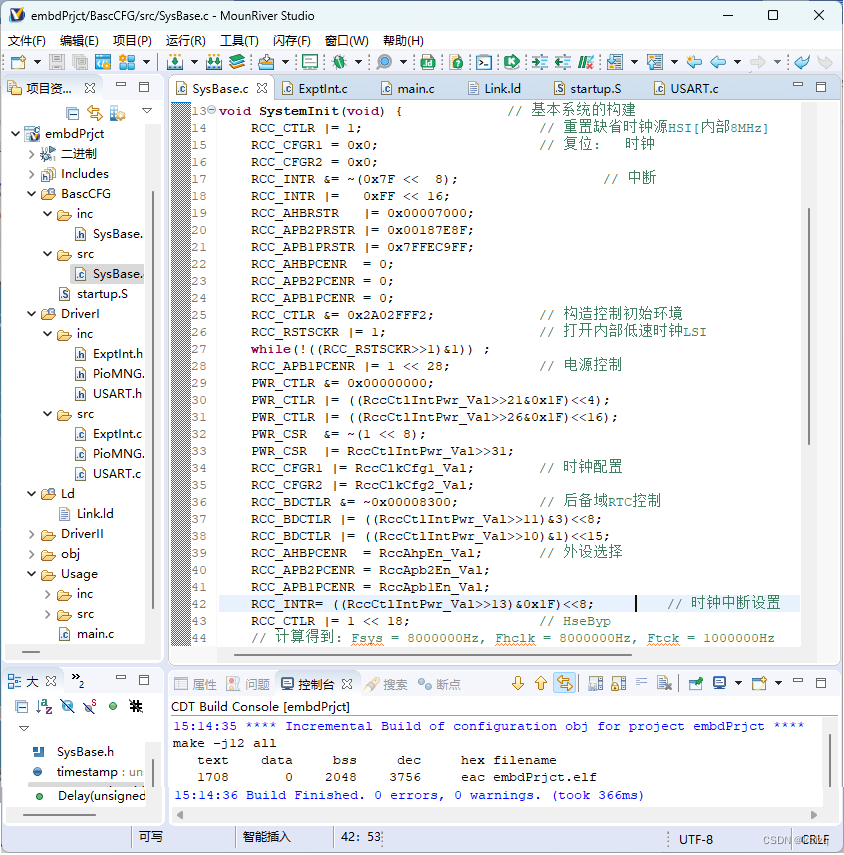

RISC-V IDE MRS使用笔记(十):嵌入式编程开发技巧汇总

RISC-V IDE MRS使用笔记(十):嵌入式编程开发技巧汇总

MRS常见嵌入式开发技巧:

Q1:如何修改程序编译生成库? A1:在工具栏中点击活动工程的编译配置按钮,在Build Artifact的Tab页面指定目标类型,选中为Stat…

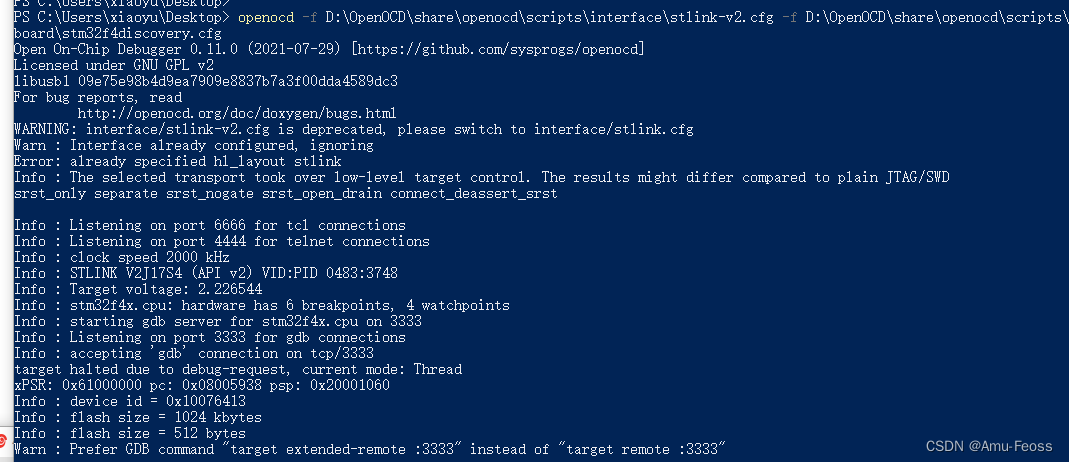

博流RISC-V芯片JTAG debug配置与运行

文章目录 1、Windows下安装与配置2、Linux下安装与配置3、芯片默认 JTAG PIN 列表4、命令行运行JTAG5、Eclipse下使用JTAG 1、Windows下安装与配置

CKLink 驱动安装

Windows版驱动下载地址: https://occ-oss-prod.oss-cn-hangzhou.aliyuncs.com/resource//1666331…

从零开始的RISC-V模拟器开发(一)环境搭建

前言

博主这系列文章是跟随中科院吴伟老师的b站公开课:[完结]从零开始的RISC-V模拟器开发第一季2021春季_哔哩哔哩_bilibili 记录的笔记。仅供学习使用,侵删!

苦逼的博主现在自己毕设也是要设计类似的东西。哎。我需要做的是给一个现成的 R…

RV32/64 特权架构

machine mode: 运行最可信的代码;supervisor mode:为 Linux,FreeBSD 和 Windows 等操作系统提供支持;user mode:权限最低,应用程序的代码在此模式下运行;

这两种新模式都比user mode有着更高的权限,有更多权限的模式通常可以使用…

体验开源香山高性能开源 RISC-V 处理器

整体架构设计

香山处理器是乱序六发射结构设计,目前支持 RV64GCBK 扩展。香山处理器前端流水线包括分支预测单元、取指单元、指令缓冲等单元,顺序取指。后端包括译码、重命名、重定序缓冲、保留站、整型/浮点寄存器堆、整型/浮点运算单元。

doc

https…

使用 C++23 从零实现 RISC-V 模拟器(4):完善 log 支持并支持更多指令

👉🏻 文章汇总「从零实现模拟器、操作系统、数据库、编译器…」:https://okaitserrj.feishu.cn/docx/R4tCdkEbsoFGnuxbho4cgW2Yntc

这一节内容解析了更多的指令,并且提供了更详细的 log 输出从而进一步的定位问题。

具体代码可以…

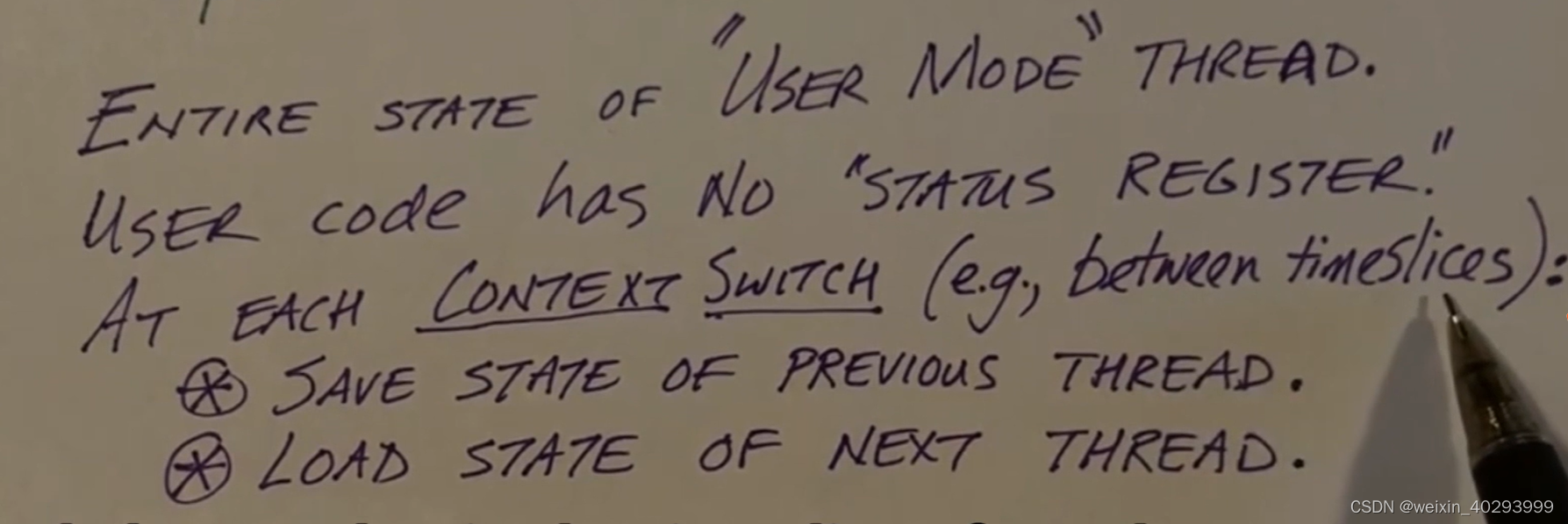

【操作系统xv6】学习记录2 -RISC-V Architecture

说明:看完这节,不会让你称为汇编程序员,知识操作系统的前置。 ref:https://binhack.readthedocs.io/zh/latest/assembly/mips.html https://www.bilibili.com/video/BV1w94y1a7i8/?p7

MIPS

MIPS的意思是 “无内部互锁流水级的微…

在WIN从零开始在QMUE上添加一块自己的开发板(二)

文章目录 一、前言往期回顾 二、CPU虚拟化(一)相关源码(二)举个例子(三)测试 三、内存虚拟化(一)相关源码(二)举个例子测试 参考资料 一、前言

笔者这篇博客…

MtimeMtimecmp

Mtime:

实时time计数器,可读可写;mtime必须按照一个固定的频率递增;如果count overflow了,则mtime的值需要卷绕;对于32/64的系统来说,mtime的值都是64bits的;

与mtime对应的,还有一…

国外芯片五大玩家联手组建了另一家RISC-V合资企业

原文链接:https://www.theregister.com/2023/08/04/chip_companies_risc_v/ 以下是正文 Initial drive starts in Germany, pushes automotive blueprints

最初的驱动从德国开始,推动汽车蓝图

The RISC-V open instruction set architecture got a boo…

LoRa无线远传水表方案ASR6500S/LLCC68

LoRa无线远传水表就是普通机械水表加上电子采集发讯模块而组成,电子模块完成信号采集、数据处理、存储并将数据通过通信线路上传给中继器、或手持式的抄表器。LoRa无线远传水表作为市面上比较火的智能水表;由主站通过传输媒体将多个户用仪表的数据集中抄…

【PWN · ret2text | RISC-V异构】[2023 羊城杯]login

第一道异构PWN的题目,没做出来。。。。但是是因为工具没有 QAQ 目录

前言

一、食用工具

Ghidra

安装使用

二、解题思路

三、exp

总结 前言

我们context.arch经常是i386和amd64,突然遇到RISC-V架构的题目,一是本地运行不了(…

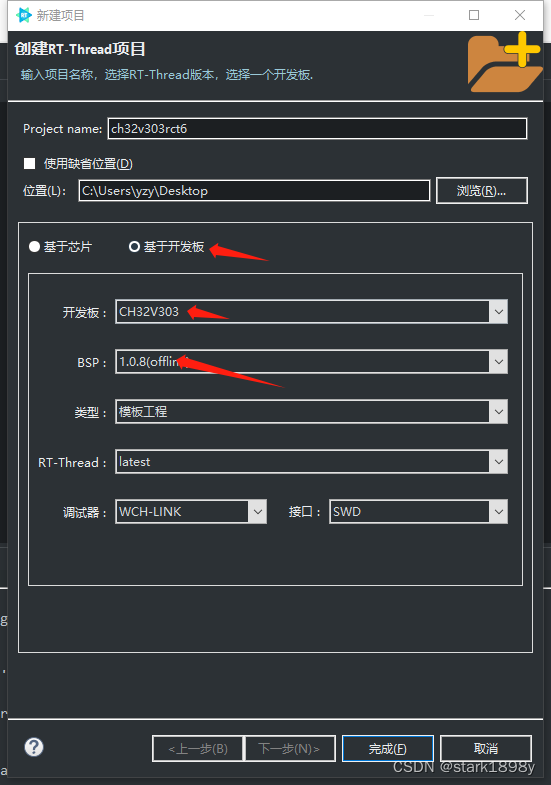

简单制作RT-Thread Studio的CH32V303的BSP支持包

简单制作RT-Thread Studio的CH32V303的BSP支持包

开原仓库链接在此:RTT_Studio_BSP_CH32V303

参考 CH32V307V-R1(V1.0.8)的 BSP,更新了外设驱动库之类的。 可以在 RT-Thread SDK 管理器中导入离线资源包,可以新建 RT…

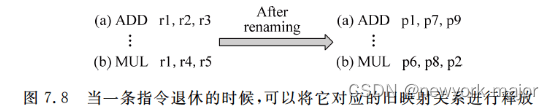

rename--统一的PRF

基本概念

将ARF/PRF进行合并,合同之后的不见,称之为统一的PRF(Physical Register File);存储的是speculative的,以及正确的(retire)寄存器值; 使用free list,存储PRF中,哪些寄存器是…

Codasip发布适用于定制计算的700系列RISC-V处理器产品

德国慕尼黑,2023年10月17日——RISC-V定制计算领域的领导者Codasip今日宣布:推出一款全新的、高度可配置的RISC-V基准性处理器系列,以实现无限创新。该系列被命名为“700系列”,包括多款应用处理器和嵌入式处理器内核。700系列通过…

Linux 中的 cd 命令及示例

cd命令在Linux 中称为更改目录命令。它用于有效地从当前工作目录移动到系统中的不同目录。

Linux 中 `cd` 命令的语法

光盘[目录]

在这里,将 [directory] 替换为您要导航到的目标目录的路径。 “cd”命令的实际实现与示例。

Linux 中的 chgrp 命令及示例

Linux 中的chgrp 命令用于更改文件或目录的组所有权。Linux 中的所有文件都属于所有者和组。您可以使用“ chown ”命令设置所有者,并使用“chgrp”命令设置组。

句法: chgrp [选项]…组文件…

chgrp [选项]… –reference=RFILE 文件…注意:首先我们需要有管理员权限才能添…

全志R128 SDK架构与目录结构

R128 S2 是全志提供的一款 M33(ARM)C906(RISCV-64)HIFI5(Xtensa) 三核异构 SoC,同时芯片内部 SIP 有 1M SRAM、8M LSPSRAM、8M HSPSRAM 以及 16M NORFLASH。本文档作为 R128 FreeRTOS SDK 开发指南,旨在帮助软件开发工程师、技术支持工程师快速上手&…

2023 RISC-V 中国峰会 演讲幻灯片和视频回放 均已公开

安全之安全(security)博客目录导读

目录

一、幻灯片地址

二、演讲视频 一、幻灯片地址:

GitHub - cnrv/RVSC2023: RISC-V Summit China 2023 二、演讲视频:

RISCV国际基金会的个人空间-RISCV国际基金会个人主页-哔哩哔哩视频 参考:CNRV …

使用 C++23 从零实现 RISC-V 模拟器(1):最简CPU

本节实现一个最简的 CPU ,最终能够解析 add 和 addi 两个指令。如果对计算机组成原理已经有所了解可以跳过下面的内容直接看代码实现。

完整代码在这个分支:lab1-cpu-add,本章节尾有运行的具体指令。

1. 冯诺依曼结构

冯诺依曼结构是现代计…

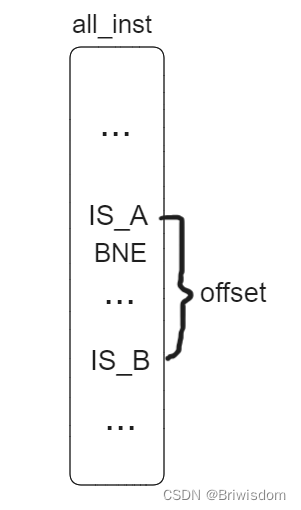

简单讲讲RISC-V跳转指令基于具体场景的实现

背景

在 RISC-V指令集中,一共有 6 条有条件跳转指令,分别是 beq、bne、blt、bltu、bge、bgeu。如下是它们的定义与接口 BEQ rs1, rs2, imm ≠ BNE rs1, rs2, imm < BLT rs1, rs2, imm ≥ BGE rs1, rs2, imm < unsigned BLTU rs1…

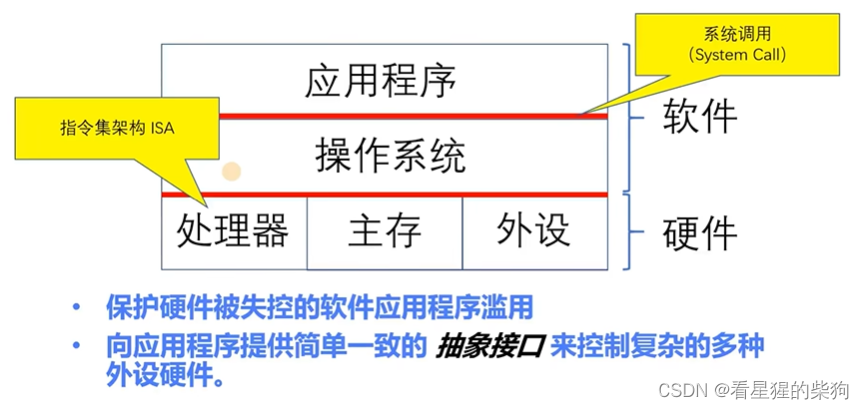

制作一个RISC-V的操作系统一-计算机系统漫游

文章目录 计算机的硬件组成两种架构程序的存储与执行程序语言的设计和进化一个mini计算机 编程语言的进化存储设备的层次结构操作系统 计算机的硬件组成

所有硬件由总线连接起来

两种架构

总线个数不同,Memory储存内容不同

程序的存储与执行

首先编译和链接某…

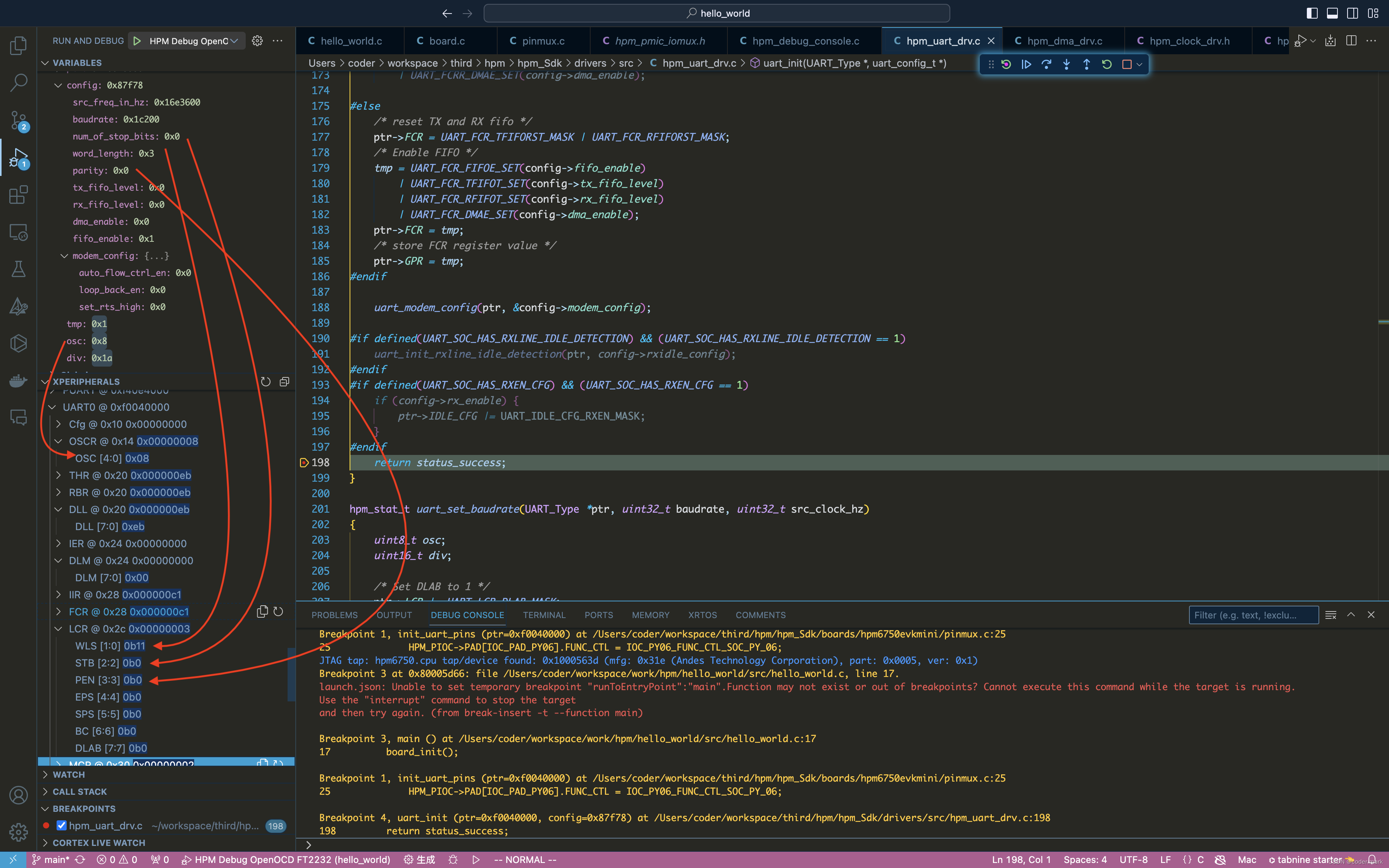

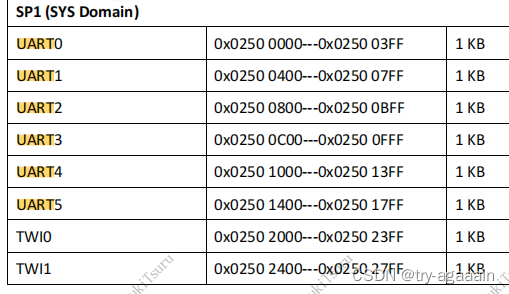

HPM6750系列--第十一篇 Uart讲解(轮询模式)

一、目的 在介绍完GPIO的相关内容下一个必须介绍的就是uart了,因为串口一个主要用途就是用于调试信息打印。 HPM6750在uart的配置上也是相当炸裂,有17个串口;结合HPM6750的高主频高内存,完全可以作为一个串口服务器。 …

【RISC-V】RISC-V寄存器简介

一、通用寄存器

32位RISC-V体系结构提供32个32位的整型通用寄存器寄存器别名全称说明X0zero零寄存器可做源寄存器(rs)或目标寄存器(rd)X1ra链接寄存器保存函数返回地址X2sp栈指针寄存器指向栈的地址X3gp全局寄存器用于链接器松弛优化X4tp线程寄存器常用于在OS中保存指向进程控…

Gemmini测试test文件chisel源码详解(二)

HeaderGenerationUnitTest.scala

源码如下:

package gemminiimport org.scalatest.FlatSpecclass HeaderGenerationUnitTest extends FlatSpec {it should "generate a header" in {println(GemminiConfigs.defaultConfig.generateHeader())}

}

Header…

制作一个RISC-V的操作系统-环境搭建

文章目录 前言环境搭配 前言

由于之前的操作系统反馈难度太大,所以准备从这个RISC-V操作系统出发,以后知识层面更加深入再去完善。

环境搭配

按照依赖项

$ sudo apt update

$ sudo apt install build-essential gcc make perl dkms git gcc-riscv64-…

邀请函|澎峰科技邀您参加CCF HPC China2023

一年一度的全球超算盛会! 以“算力互联智领未来”为主题的第十九届全国高性能计算学术年会(CCF HPC China 2023)将于8月24-26日(展览23-25日)在青岛红岛国际会议展览中心举办。

九大院士领衔 打造顶级超算盛会

力邀…

RISC-V是如何与X86、ARM三分天下

目录

1.行业CPU指令集格局

2.汽车中的RISC-V进展

2.1 国际进展

2.2 国内进展

3.小结 2023年3月2日,在平头哥牵头举办的玄铁RISC-V生态大会上,工程院院士倪光南表示,基于RISC-V模块化、可扩展、容易定制、不受垄断制约等优势,…

ISSUE的基本概念

ISSUE:将符合一定条件的指令从发射队列(IssueQueue)中选出来,并送到FU中执行的过程;

ISSUE QUEUE也称之为reservation station, 其按照一定的规则,选择那些源操作数都已经准备好的指令,将其送到FU中执行,这个过程称为…

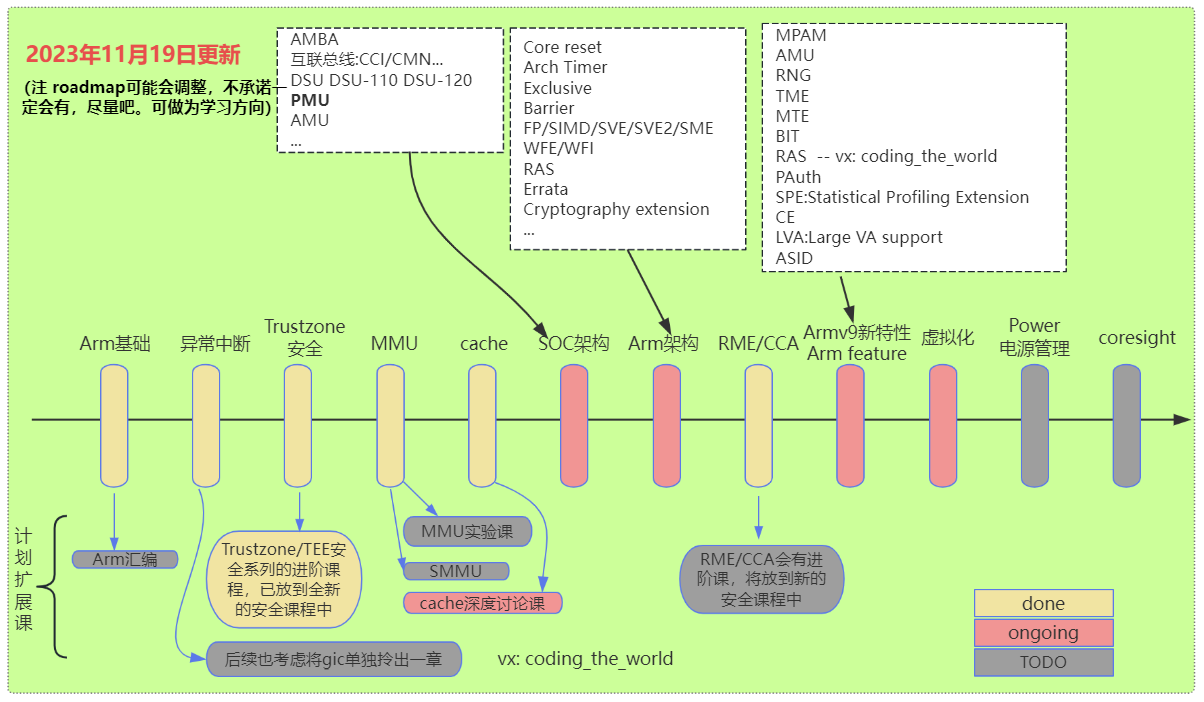

拒绝烂尾,Arm二期持续更新中,Arm二期Roadmap

感谢大家的支持,感谢大家一直以来的鼓励。更感谢大家的包容。近期又更新了很多课程,这次都是总线和协议相关的,适合软件同学基础扫盲。 硬件的同学请自行考虑,相信你们研究的比我这深。同时呢也在规划一些直播讨论交流课ÿ…

操作系统基础知识介绍之并行技术(包括指令级并行和数据级并行以及线程级并行和请求级并行)

一、相关概念

1.1 指令级并行

指令级并行是指在一个处理器内部,利用流水线、超标量、乱序执行等技术,使得多条指令可以同时或部分重叠地执行,从而提高指令的执行速度。比如,一个四级流水线可以同时执行四条指令的不同阶段&#…

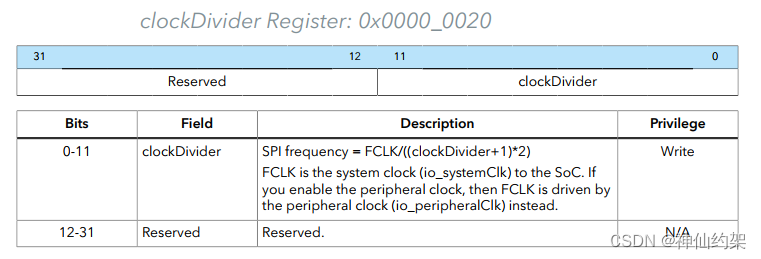

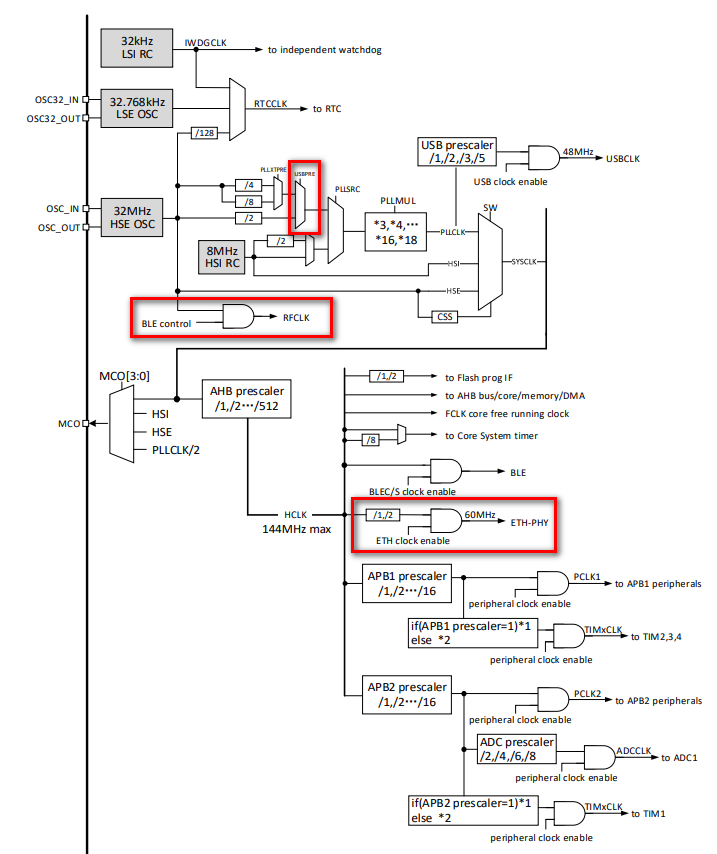

沁恒CH32V307使用记录:SPI基础使用

文章目录目的基础说明使用演示其它补充总结目的

SPI是单片机中比较常用的一个功能。这篇文章将对CH32V307中相关内容进行说明。

本文使用沁恒官方的开发板 (CH32V307-EVT-R1沁恒RISC-V模块MCU赤兔评估板) 进行演示。

基础说明

SPI的基础概念见下面文…

RISC-V 嵌入式 Rust 快速入门,基于 Renode 模拟器和 HiFive1 开发板

配置开发环境

这里以 Ubuntu 18.04 作为宿主环境,其它 Linux 发行版类似。Windows 环境待更新。

安装标准 Rust 编译器

wget https://cdn.jsdelivr.net/gh/rust-lang-nursery/rustup.rs/rustup-init.sh

export RUSTUP_DIST_SERVERhttps://mirrors.ustc.edu.cn/ru…

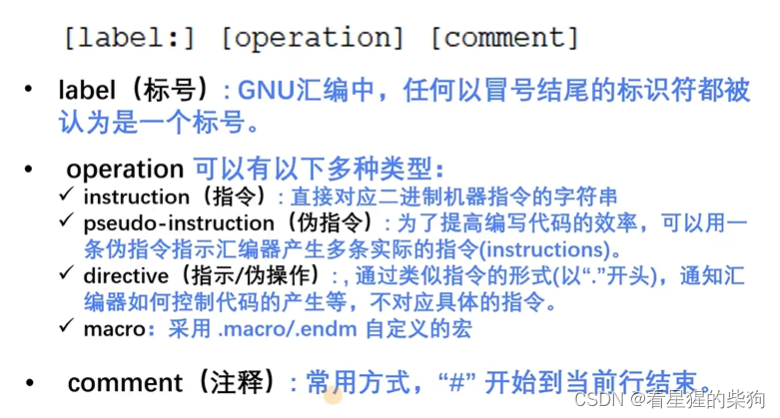

制作一个RISC-V的操作系统五-RISC-V汇编语言编程一

文章目录 RISC-V汇编语言入门汇编语言概念简介 汇编语言语法介绍(GNU版本) RISC-V汇编语言入门

汇编语言概念简介

高级:可以理解就是更贴近人的理解 低级:可以理解就是更贴近机器的

难移植:汇编指令基本上和机器指令…

【RISC-V DSP设计】基于CEVA DSP架构的指令集分析(二)-函数列表

目录

表3-1:定点滤波器功能

表3-2:定点快速傅里叶变换(FFT)函数

表3-3:定点数学函数

表3-4:定点三角函数

表3-5:定点向量函数

表3-6:定点矩阵函数

表3-7:浮点滤波…

在UBUNTU上使用Qemu和systemd-nspawn搭建RISC-V轻量级用户模式开发环境

参考链接

使用Qemu和systemd-nspawn搭建RISC-V轻量级用户模式开发环境 - 知乎

安装Qemu

sudo apt updatesudo apt -y install qemu-user-binfmt qemu-user-static systemd-container

sudo apt -y install zstd

配置环境

RISCV_FILEarchriscv-2023-10-09.tar.zstwget -c ht…

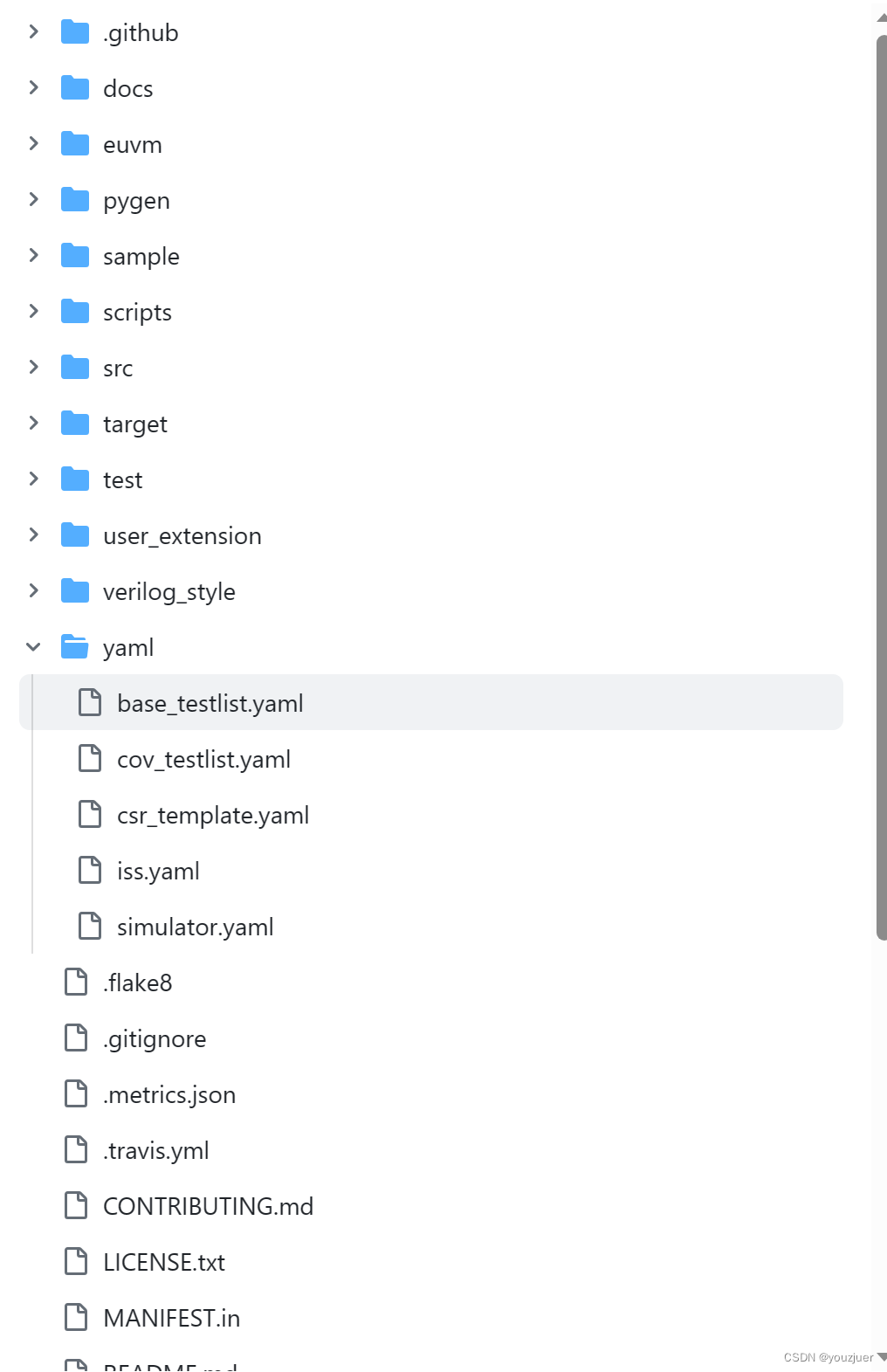

risc-v dv源代码分析

地址为

GitHub - chipsalliance/riscv-dv: Random instruction generator for RISC-V processor verificationRandom instruction generator for RISC-V processor verification - GitHub - chipsalliance/riscv-dv: Random instruction generator for RISC-V processor verif…

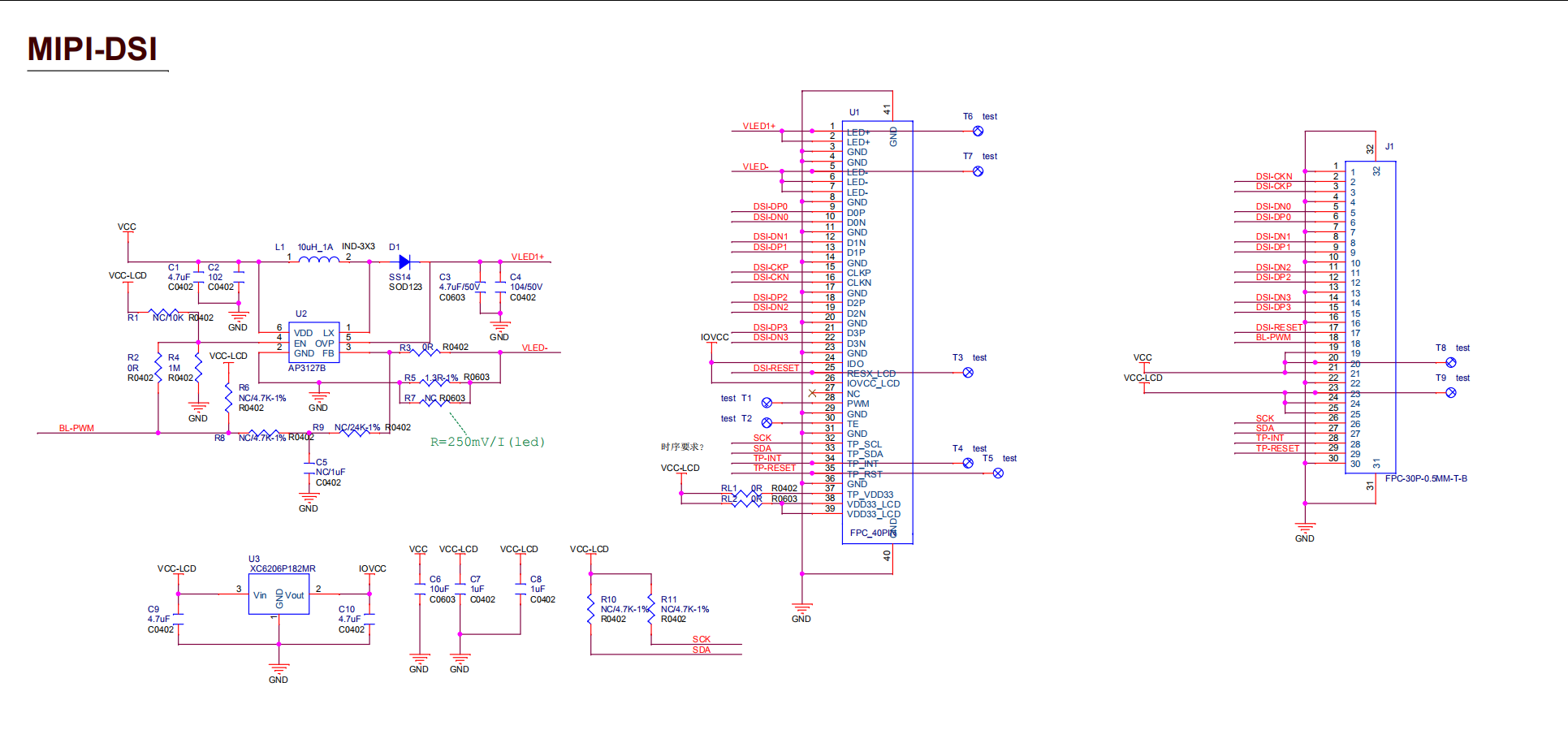

全志D1芯片 MIPI屏幕TFT08006支持

屏幕简介

TFT08006官方支持的一款MIPI屏幕,8寸,分辨率800*1280。官方套装支持触控。 下载

MIPI屏幕 TFT08006 patch: https://www.aw-ol.com/downloads/resources/27

MIPI屏幕 TFT08006 相关资料见:https://www.aw-ol.com/down…

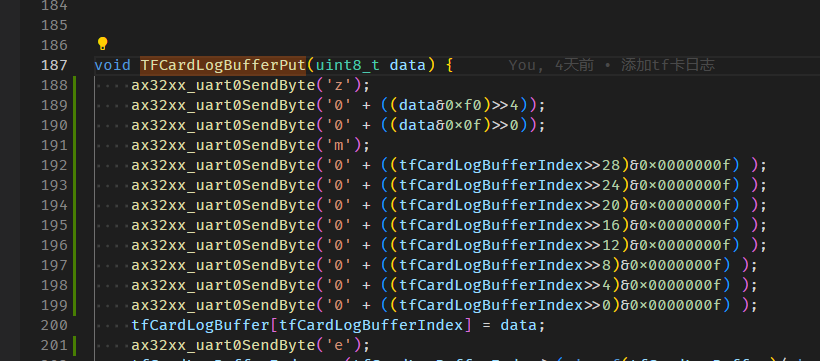

踩坑记 BSS段的初始化

title: 踩坑记 BSS段的初始化 category_bar: true categories:

blog tags:embedded date: 2023-10-20 19:23:05 前言

接手一个项目,调试全靠串口日志,测试同事测试产品的时候无法拿到日志,刚好产品RAM够大,且刚好有SD卡。所以就…

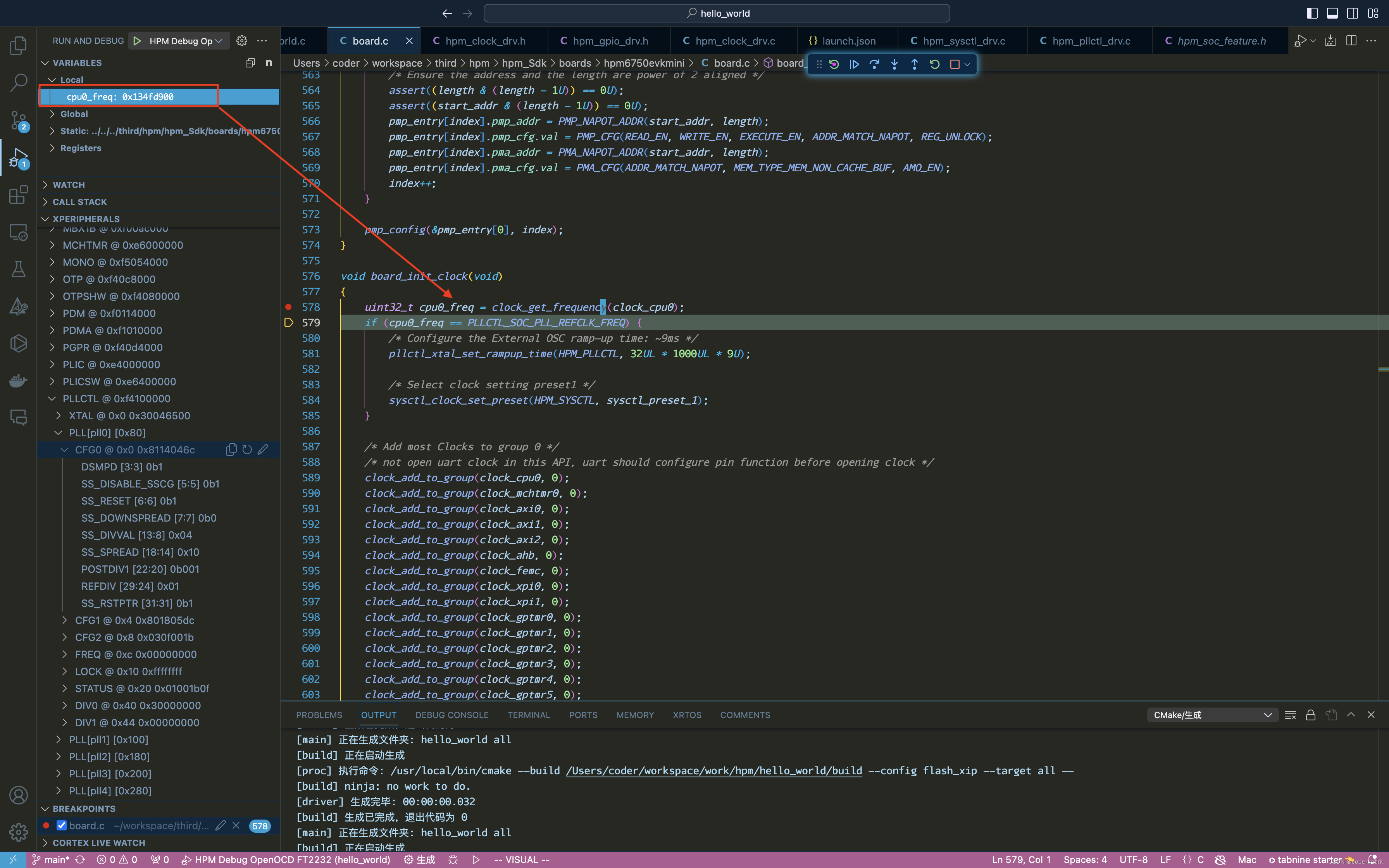

HPM6750系列--第十篇 时钟系统

一、目的 上一篇中《HPM6750系列--第九篇 GPIO详解(基本操作)》我们讲解了HPM6750 GPIO相关内容,在进一步讲解其他外设功能之前我们有必要先讲解一下HPM6750的时钟系统。 时钟可以说是微控制器系统中的心脏,片上外设模块必须依赖时…

RISC-V Assembler Modifiers

原始内容如下: RISC-V Assembler Modifiers The RISC-V assembler supports following modifiers for relocatable addresses used in RISC-V instruction operands. However, we also support some pseudo instructions that are easier to use than these modifie…

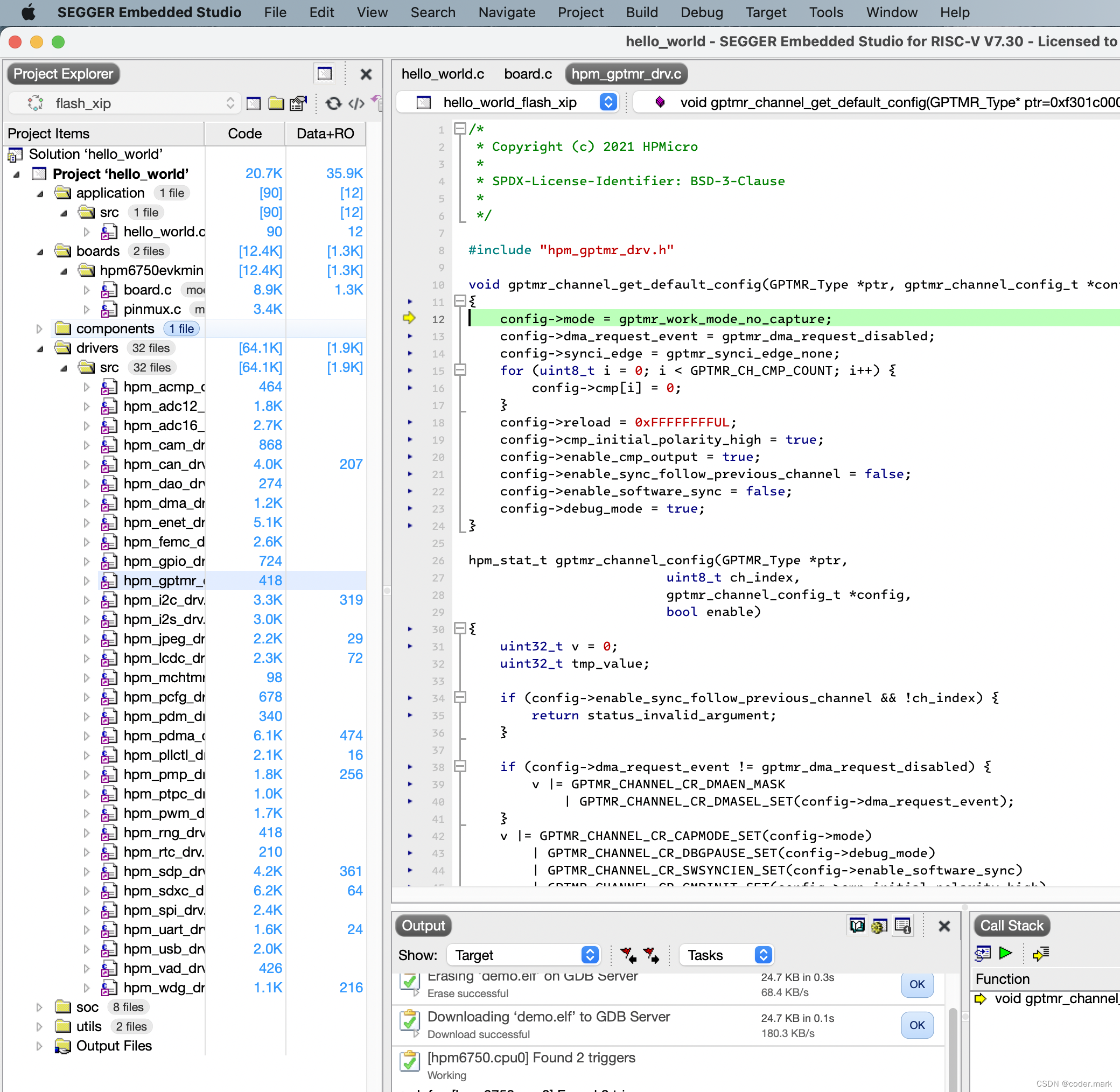

HPM6750系列--第五篇 使用Segger Embedded Studio for RISC-V开发环境

一、目的 之前的博文中《HPM6750系列--第四篇 搭建Visual Studio Code开发调试环境》我们介绍了如何使用visual studio code进行开发调试,但是用起来总缺少点感觉,那么有没有更加友好一些的IDE用来开发呢? 本篇主要介绍如何使用Embedded Stud…

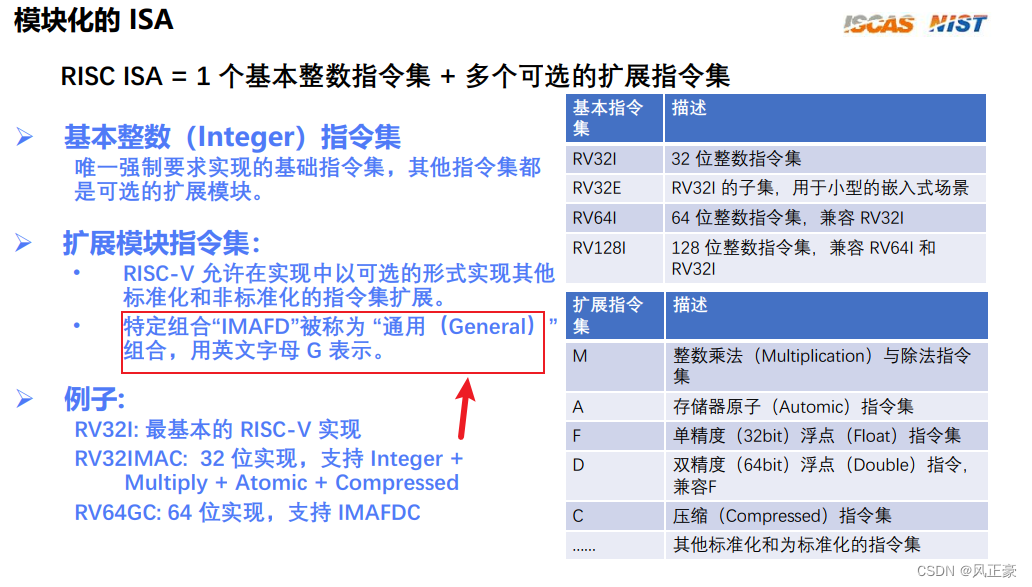

制作一个RISC-V的操作系统二-RISC-V ISA介绍

文章目录 ISA的基本介绍啥是ISA为什么要设计ISACISCvsRISCISA的宽度知名ISA介绍 RISC-V历史和特点RISC-V发展RISC-V ISA 命名规范模块化的ISA通用寄存器Hart特权级别Control and Status Register(CSR)内存管理与保护异常和中断 ISA的基本介绍

啥是ISA

…

RISC-V搭建嵌入式QT开发环境

安装环境: Ubuntu18.04 GCC:gcc version 7.5.0 (Ubuntu 7.5.0-3ubuntu1~18.04) CROOSS-tools:gcc version 8.3.0 (crosstool-NG 1.24.0)

下载5.12安装包,解压后修改qmake.conf配置参数,将编译工具修改为交叉编译器

/qt-everywhere-src-5.12.12$ vi qtbase/mkspecs/linux…

riscv 各种版本 gcc 工具链编译与安装

riscv 各种版本 gcc 工具链编译与安装

riscv gcc工具下载

Riscv 的 gcc 交叉编译器,以开源的方式托管在 github 上。链接如下:

https://github.com/riscv/riscv-gnu-toolchain 该仓库,里面包含了一些子仓库。

使用以下这个命令࿰…

RISC-V常用汇编指令

RISC-V寄存器表:

RISC-V和常用的x86汇编语言存在许多的不同之处,下面将列出其中部分指令作用:

指令语法描述addiaddi rd,rs1,imm将寄存器rs1的值与立即数imm相加并存入寄存器rdldld t0, 0(t1)将t1的值加上0,将这个值作为地址,取…

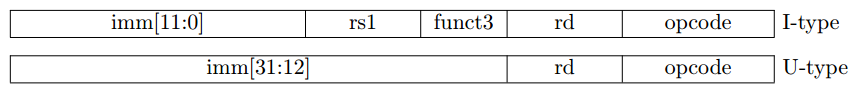

可以跑Linux的RISC-V计算机、微型电脑、单板机

目前国内能买到的有:RVBoards-D1-哪吒,玄铁C906,699RMB。VisionFive 昉星光,U74双核,1100RMB。PicoRio 放出了图纸。

RVBoards-D1-哪吒

使用体验

购买方便,某宝有售,搜索 rvboards 即可。玄铁…

RISC-V IDE MRS无感远程协助模块详解

RISC-V IDE MRS无感远程协助模块详解

一、说明

1.1 概述 针对RISC-V/ARM等内核MCU的嵌入式集成开发环境MRS(MounRiver Studio)从V1.90版本开始内置无感远程协助模块(Sensorless Remote Assistant Module,以下简称SRA模块)。SRA模块是一款支…

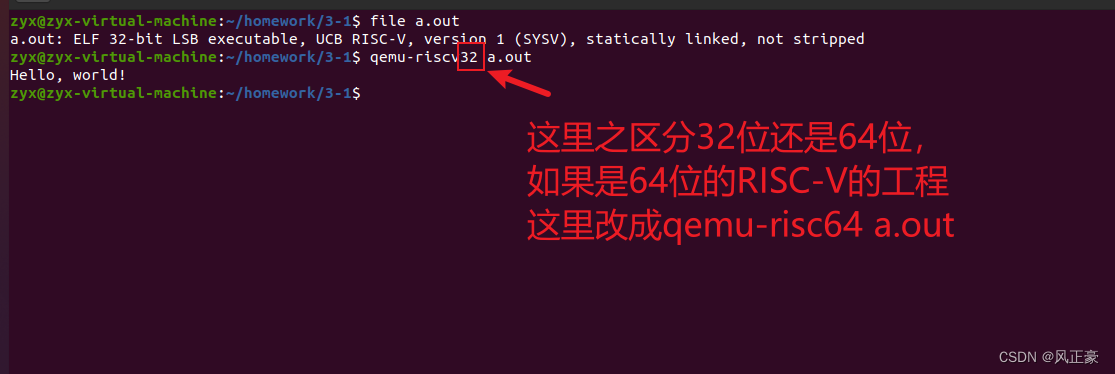

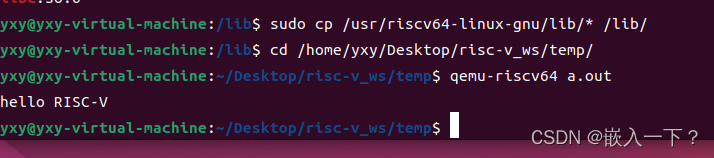

qemu-riscv64: could not open ‘/lib/ld-linux-riscv64-lp64d.so.1‘

问题

缺少文件,或者说文件下载到了一个调用不到的地方

解决办法

先把对应的库下载好 sudo apt install libc6-riscv64-cross

sudo apt install binutils-riscv64-linux-gnu

sudo apt install gcc-riscv64-linux-gnu

sudo apt install binutils-riscv64-unknown-e…

RISC-V交叉工具链riscv-gnu-toolchain编译

文章目录 1、下载2、编译1. 依赖安装2. 编译 3、运行 1、下载

$ sudo apt-get install git wget build-essential

$ git clone https://github.com/riscv-collab/riscv-gnu-toolchain

$ git checkout 2023.06.02注意上面 clone 的仓库,我们称其为构建脚本仓库&…

使用 C++23 从零实现 RISC-V 模拟器(2):内存和总线

内存和总线

上一部分将内存全部放到了 CPU 里面,总线的概念是隐含着的。这一部分将内存拆分出来,再引入总线的概念,CPU 通过总线连接内存。

完整代码可以查看这个分支:https://github.com/weijiew/crvemu/tree/lab2-memory

实际…

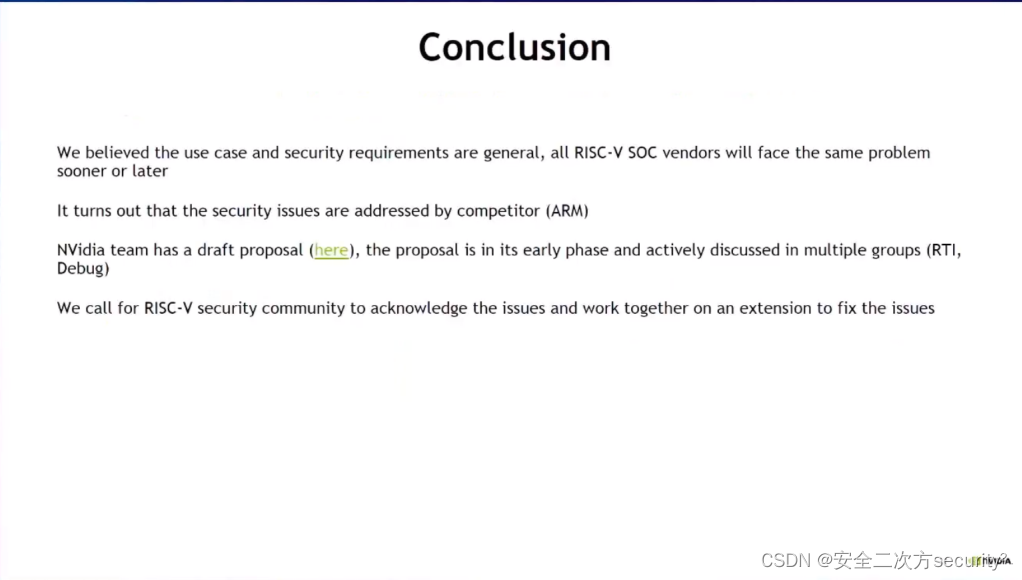

RISC-V IOPMP实际用例-Rapid-k模型在NVIDIA上的应用

安全之安全(security)博客目录导读

2023 RISC-V中国峰会 安全相关议题汇总 说明:本文参考RISC-V 2023中国峰会如下议题,版权归原作者所有。

RISC-V声名鹊起,究竟为何?

近期,高通、恩智浦、Nordic、博世和英飞凌等宣布联手组建一家芯片新公司,目标是通过支持下一代硬件开发而推动RISC-V在全球范围内实现。该公司将支持基于RISC-V的兼容产品、提供参考架构并帮助建立行业广泛使用的解决方案,应用重点包括汽车、…

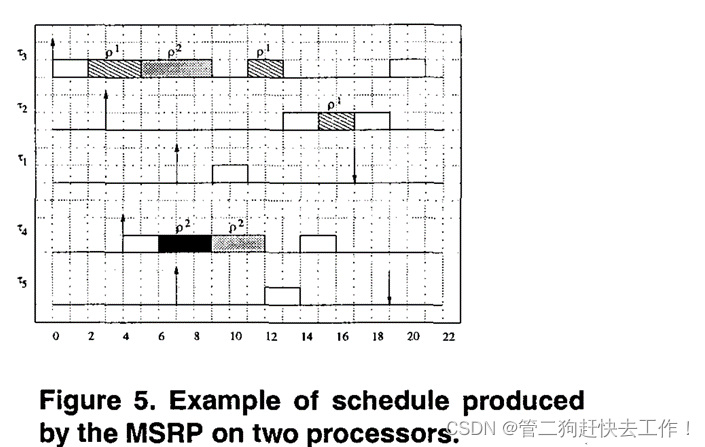

操作系统论文导读(四):Minimizing Memory Utilization of Real-Time Task Sets in Single and…

目录

一、论文核心思想:

二、降低RAM的思想

三、基本的相关定义

四、单处理器方面

五、优化单处理器中的堆栈使用

六、多处理器方面

七、基本的相关调度

八、协议特点 Minimizing Memory Utilization of Real-Time Task Sets in Single and Multi-Processor…

RISC-V ELF规范和函数调用规范

原文出处:https://github.com/riscv-non-isa/riscv-elf-psabi-doc/blob/master/riscv-cc.adoc

psABI: Processor Specific Application Binary Interface

RISC-V ELF psABI specification

Table of Contents

Register Convention Integer Register ConventionFl…

RISC-V Linux_kernel制作

文章目录 1、下载2、编译 1、下载

Linux 官网地址:https://www.kernel.org

$ wget https://cdn.kernel.org/pub/linux/kernel/v5.x/linux-5.10.181.tar.xz

$ tar xvf linux-5.10.181.tar.xz

$ cd linux-5.10.1812、编译

安装依赖

$ sudo apt-get install -y flex bison bui…

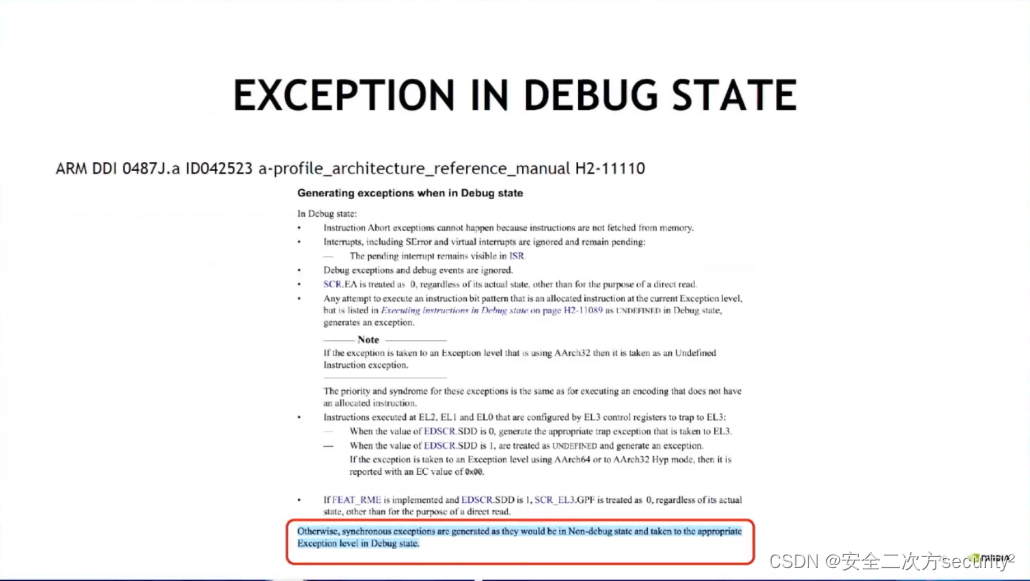

基于硬件隔离增强risc-v调试安全1_问题描述

安全之安全(security)博客目录导读

2023 RISC-V中国峰会 安全相关议题汇总 说明:本文参考RISC-V 2023中国峰会如下议题,版权归原作者所有。

RISC-V中国峰会 | 256核服务器高调亮相,谁与争锋?

8月23日,第三届RISC-V中国峰会(RISC-V Summit China 2023)在北京香格里拉饭店正式开幕,来自世界各地的行业精英汇聚一堂,为RISC-V生态系统建言献策,凝心聚力!

中国工程院院士倪光南、RISC-V国际…

大道至简——RISC-V架构之魂(下)

本文为《RISC-V CPU设计》专栏和《RISC-V嵌入式软件开发》专栏系列文章之一。 注:本文节选自“硅农亚历山大”所著国内第一本系统介绍CPU与RISC-V设计的中文书籍《手把手教你设计CPU:RISC-V处理器篇》(预计将于2018年3~4月上市)。…

RISC-V为微控制器应用考虑的特性

RISC-V是加州大学伯克利分校(UC Berkeley)推出的开源处理器架构。RISC-V的设计具有极强的伸缩性,可以应用在从微控制器到集群计算机等各种级别的应用。我是搞嵌入式的,比较关注RISC-V在微控制器上的应用。

mingdu.zheng at gmail…

2.5 opensbi: riscv: opensbi源码解析

文章目录 4.15 sbi_hsm_prepare_next_jump()函数4.16 sbi_hart_switch_mode()函数5. 异常处理分析5.1 中断处理5.1.1 timer处理函数5.1.2 ipi中断处理函数5.2 异常处理4.15 sbi_hsm_prepare_next_jump()函数 函数位置:lib/sbi/sbi_hsm.c 函数参数 函数作用:设置所有hart状态为…

Si24R03—低功耗 SOC 芯片(集成RISC-V内核+2.4GHz无线收发器)

Si24R03是一款高度集成的低功耗SOC芯片,其集成了基于RISC-V核的低功耗MCU和工作在2.4GHz ISM频段的无线收发器模块。 MCU模块具有低功耗、Low Pin Count、宽电压工作范围,集成了13/14/15/16位精度的ADC、LVD、UART、SPI、I2C、TIMER、WUP、IWDG、RTC等丰…

6.S081——补充材料——RISC-V架构中的异常与中断详解

0.briefly speaking

我在阅读Xv6源码过程中对很多概念感到困惑,想到也许会有其他人对此秉持同样的困惑,所以我将我的研究和学习过程总结下来并编篡成如下的博客。本篇博客想对RISC-V标准中有关中断和异常的概念进行一个梳理,考虑RISC-V标准的…

制作一个RISC-V的操作系统五-RISC-V汇编语言编程三

文章目录 分析code/asm/add中的makefile相关命令 算数运算指令addadd2sub 练习5-1 分析code/asm/add中的makefile

makefile

EXEC testSRC ${EXEC}.sGDBINIT ../gdbinitinclude ../rule.mk很明显还要去执行rule.mk

rule.mk

include ../../common.mk.DEFAULT_GOAL : all

a…

RISC-V公测平台发布 · 7-zip 测试

简介

7-Zip 是一个开源的压缩和解压缩工具,具有高压缩比和快速解压缩的特点。除了普通的文件压缩和解压缩功能之外,7-Zip 还提供了基准测试功能,通过压缩和解压缩大型文件来评估系统的处理能力和性能。

7-Zip 提供了一种在不同压缩级别和多…

RISC-V架构——中断委托和中断注入

1、中断委托

1.1、中断委托的作用 (1)默认情况下,所有的陷入(中断和异常)都是在M模式下处理,然后再返回到发生陷入前的模式; (2)所有陷入都在M模式处理会涉及到模式切换…

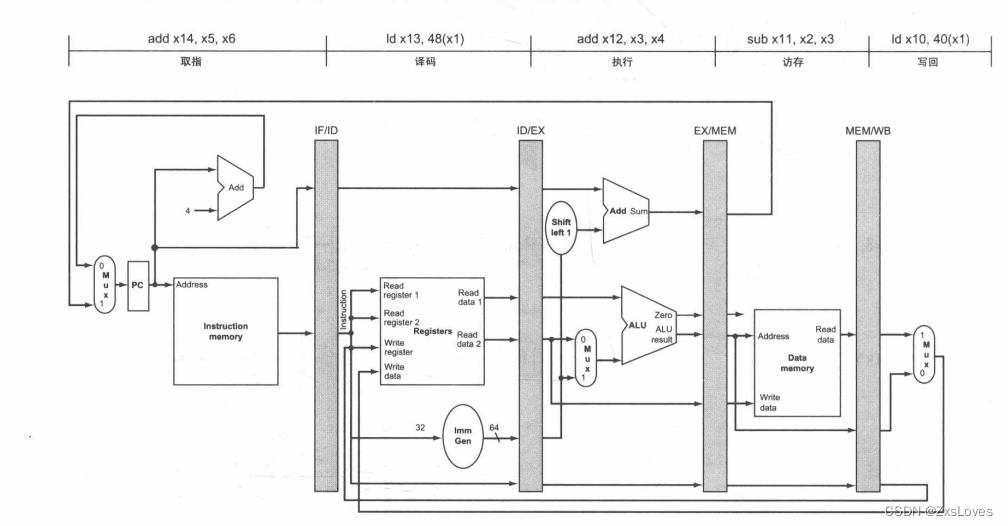

RISC-V 流水线 CPU 设计 Verilog

实验设计的是五段式流水线 CPU,分别为 IF(取指),ID(指令译码),EX(执行),MEM(访存),WB(写回)五个阶…

RISC-V 编译环境搭建:riscv-gnu-toolchain 和 riscv-tools

RISC-V 编译环境搭建:riscv-gnu-toolchain 和 riscv-tools

编译环境搭建以及说明

操作系统:什么系统都可以

虚拟机:VMmare Workstation Pro 17.50.x (版本不限)

编译环境:Ubuntu 18.04.5

CPU:i7-8750h(虚拟机分配4核…

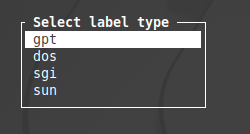

Linux 中的 cfdisk 命令及示例

cfdisk命令用于在磁盘设备上创建、删除和修改分区。它通过提供基于文本的“图形”界面来显示或操作磁盘分区表。

cfdisk /dev/sda

示例: 运行后您会收到如下提示:从列表中

RISC-V嵌入式开发入门篇1:RISC-V GCC工具链的介绍

原文出处:https://mp.weixin.qq.com/s/QayXAQPkOcpeEMbOwPa1Ww 随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》正式上市,越来越多的爱好者开始使用开源的蜂鸟E203 RISC-V处理核,很多初学者留言询问有关RISC-V工具链使…

【【萌新的RISCV学习之流水线通路的控制-8】】

萌新的RISCV学习之流水线通路的控制-8

我们在之前学习了整个单周期的模块工作流程

我们按照整体的思路分段 将数据通路划分为5个阶段 IF : 取地址 ID :指令译码和读存储器堆 EX :执行或计算地址 MEM : 数据存储器访问 WB : 写回

单周期数据通路&…

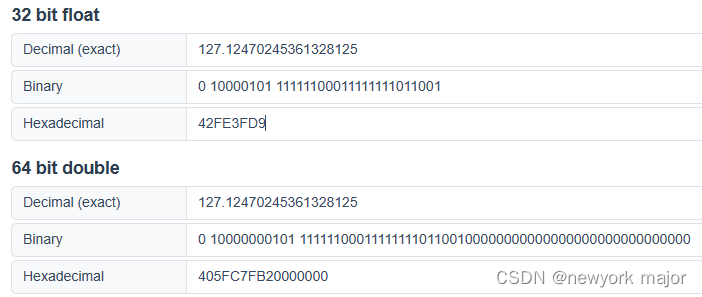

浮点数的转换--IEEE 754

IEEE754标准是一种浮点数表示标准,一般分为

单精度(32位的二进制数);双精度(64位的二进制数)

根据国际标准IEEE754,任意一个二进制浮点数V可以表示为下面形式:

V (-1)^s *&#…

读书·基于RISC-V和FPGA的嵌入式系统设计·第3章

72.8051单片机的弊端和指令集架构CISC的缺点

76.RV指令集的特征(⭐) 特权架构和特权指令集是相关但不完全相同的概念。 特权架构(Privileged Architecture)指的是计算机体系结构中用于实现特权级操作的硬件和软件机制。特权架构定…

沁恒 CH32V208(一): CH32V208WBU6 评估板上手报告和Win10环境配置

目录

沁恒 CH32V208(一): CH32V208WBU6 评估板上手报告和Win10环境配置

CH32V208

CH32V208系列是沁恒32位RISC-V中比较新的一个系列, 基于青稞RISC-V4C内核, 最高144MHz主频, 64KB SRAM,128KB Flash, 供电电压2.5/3.3V.

这个型号的特点: 除了特有的硬件堆栈区、…

risc-v异常处理

异常与中断的关系

中断和异常都为异常,分为:

同步异常:IO,illegal, page fault,miss_aligh 等来自处理器内部的发生的异常。异步异常(中断):鼠标,键盘,Time…

PULP Ubuntu18.04

1. 安装eda工具:questasim_10.7_linux64,网上有教程和方法,如有问题,可私信我

2. 代码下载:

git clone https://github.com/pulp-platform/pulp 编译代码 cd pulp source setup/vsim.sh make checkout make scripts …

(一)RISC-V 指令集及寄存器介绍

1. RISC-V指令集介绍

RISC-V 念作 “risk-five”,代表着 Berkeley 所研发的第五代精简指令集。 该项目 2010 年始于加州大学伯克利(Berkeley)分校,希望选择一款 ISA用于科研和教学。经过前期多年的研究和选型,最终决定…

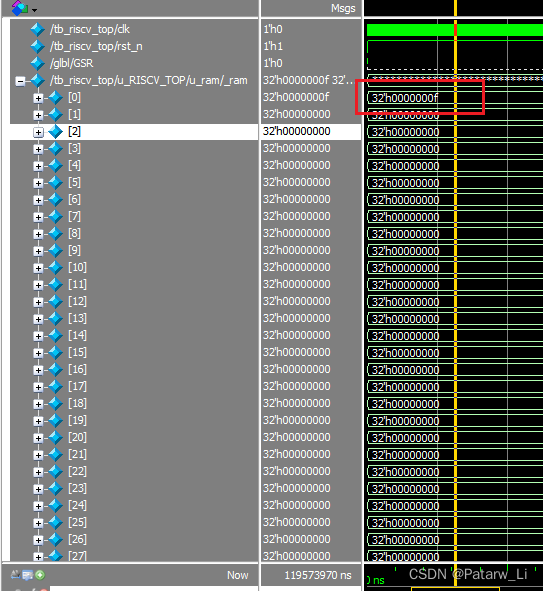

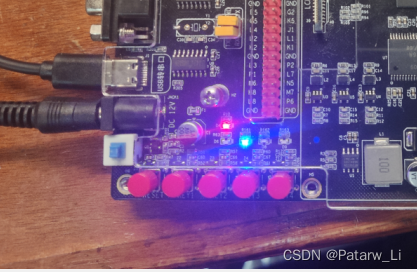

RISC-V处理器的设计与实现(三)—— 上板验证(基于野火征途Pro开发板)

文章目录

RISC-V处理器的设计与实现(一)—— 基本指令集_Patarw_Li的博客-CSDN博客

RISC-V处理器的设计与实现(二)—— CPU框架设计_Patarw_Li的博客-CSDN博客

RISC-V处理器的设计与实现(三)—— 上板验…

Linux stat 命令及示例

介绍

该stat命令打印有关文件和文件系统的详细信息。该工具提供有关所有者是谁、修改日期、访问权限、大小、类型等信息。

该实用程序对于故障排除、在更改文件之前获取有关文件的信息以及例行文件和系统管理任务至关重要。

本文stat通过实际示例解释了有关 Linux 命令的所有…

RISC-V公测平台发布· CoreMark测试报告

一. CoreMark简介

CoreMark是一款用于评估CPU性能的基准测试程序,它包含了多种不同的计算任务,包括浮点数、整数、缓存、内存等方面的测试。CoreMark的测试结果通常被用来作为CPU性能的参考,它可以帮助开发人员和系统管理员评估不同处理器和…

Cortex-M与RISC-V区别

环境

Cortex-M以STM32H750为代表,RISC-V以芯来为代表

RTOS版本为RT-Thread 4.1.1 寄存器 RISC-V 常用汇编

RISC-V

关于STORE x4, 4(sp)这种寄存器前面带数字的写法,其意思为将x4的值存入sp4这个地址,即前面的数字表示偏移的意思

反之LOA…

使用gdb调试QEMU模拟的RISC-V平台程序

我们跑一个裸核程序,也就是不带操作系统的程序,然后使用gdb调试该程序。

首先编译目标程序,然后使用QEMU的kernel参数进行加载

qemu-system-riscv64 -s -S -bios opensbi.elf -m 4G -smp 4 -kernel my_program.x -nographic

-s 让QEMU在12…

RISC-V架构——物理内存属性和物理内存保护

1、物理内存属性(PMA:Physical Memory Attributes) (1)系统内存映射包含各种不同属性的地址空间范围,每个地址空间范围支持的操作不一样; (2)物理内存属性一般是在芯片设…

共话开源 - openKylin出席 FOSSASIA Summit 2023 开源盛会!

4月14日,openKylin社区受邀参加FOSSASIA Summit 2023开源盛会,给来自全球的技术开发者带来openKylin社区在RISC-V软硬件生态建设方面的经验与成果介绍,向大家展示中国开源社区的潜力,并同国际技术社区共研RISC-V未来之势。

FOSSA…

在Lichee RV Dock上的不成功的烧录尝试

最近在学基于risc-v的简单操作系统,刚好手里有块Lichee RV Dock 的板子,所以在学了基础的"hello, world"程序后,想着能不能把这个程序烧录到板子上,简单的做个实验。

要完成这个任务,需要将程序烧录到sd卡上…

鉴释宣布加入RISC-V基金会、Linux基金会、seL4基金会与IoXt联盟,旨在实现静态代码分析服务的全方位赋能

2021年7月27日,中国深圳——近日,静态代码工具开发商鉴释科技(下文简称:鉴释)宣布其加入RISC-V基金会、Linux基金会、seL4基金会,以及IoXt联盟四大国际非盈利组织。此次加入芯片、开源操作系统、操作系统微…

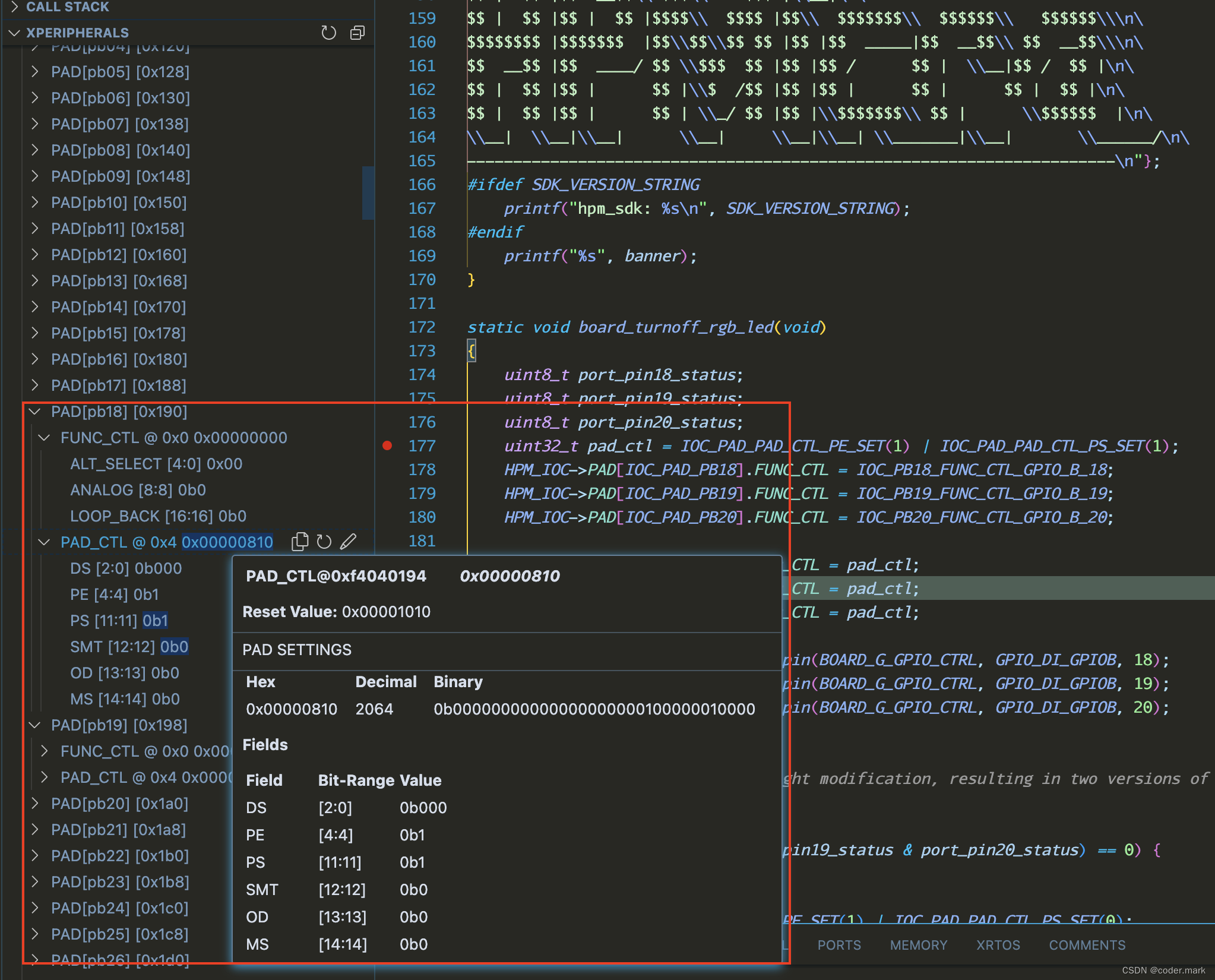

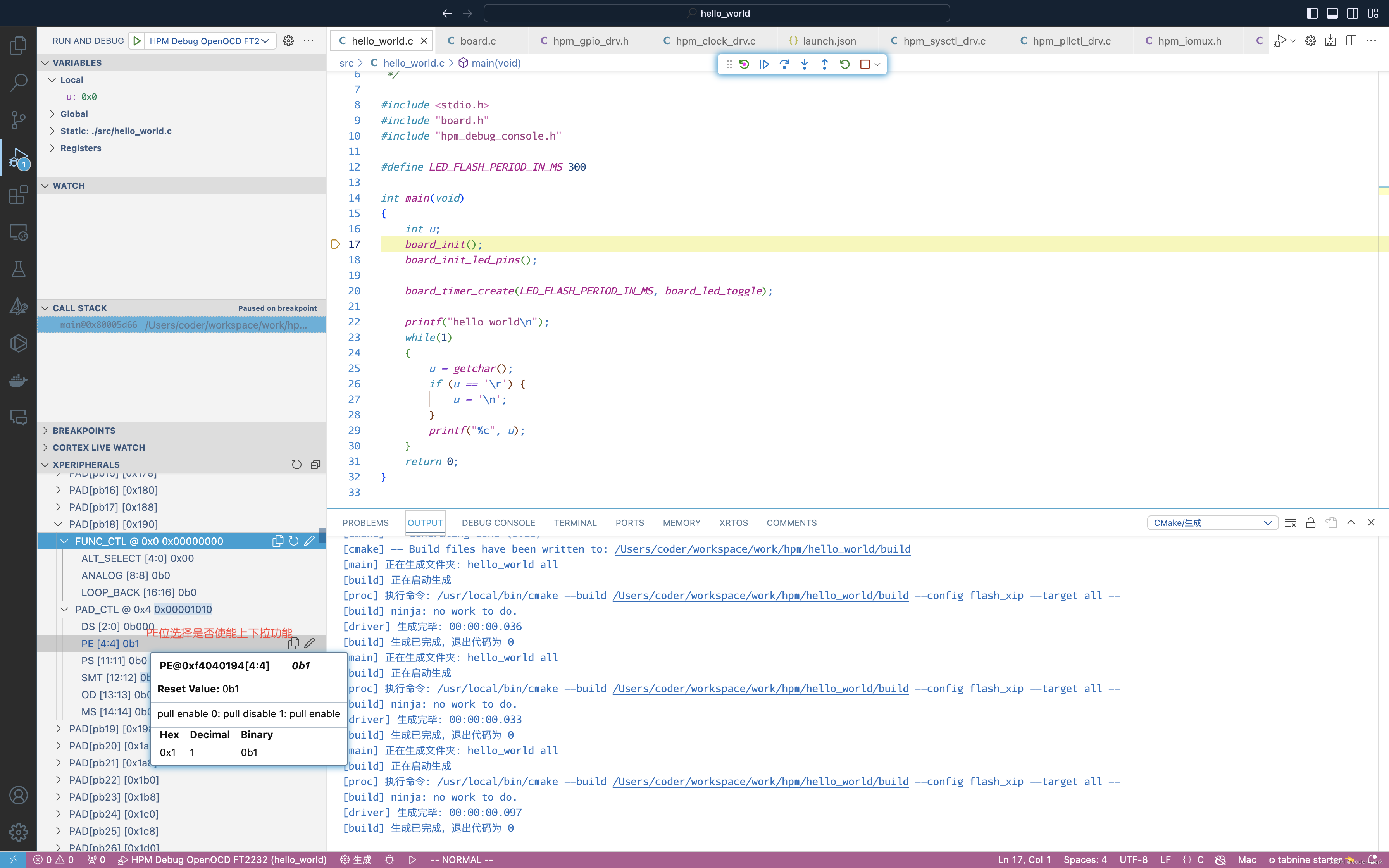

HPM6750系列--第七篇 Visual Studio Code使用openocd调试查看外设信息

一、目的 在《HPM6750系列--第四篇 搭建Visual Studio Code开发调试环境》我们已经手把手指导大家如何在visual studio code中进行开发,包括编译调试等步骤以及相关配置文件。 但是在实际调试时发现找不到芯片寄存器实时显示的窗口,本篇主要讲解如何实现…

issue unit

The Issue Unit

issue queue用来hold住,已经dispatched,但是还没有执行的uops;

当一条uop的所有的operands已经ready之后,request请求会被拉起来;然后issue select logic将会从request bit 1的slot中,选择…

RISC-V基础指令之addi与lui(生成一个更大的立即数,包含负数符号拓展的特殊情况)

这两条指令都是RISC-V体系结构中的整数指令,它们的功能和格式如下: lui指令的全称是Load Upper Immediate,它的功能是把一个20位的立即数加载到寄存器的高20位,低12位为0。它的格式是: lui rd, imm 其中,rd…

【risc-v】易灵思efinix FPGA riscv 时钟配置的一些总结

系列文章目录

分享一些fpga内使用riscv软核的经验,共大家参考。后续内容比较多,会做成一个系列。

本系列会覆盖以下FPGA厂商 易灵思 efinix 赛灵思 xilinx 阿尔特拉 Altera

本文内容隶属于【易灵思efinix】系列。 文章目录 系列文章目录前言一、pan…

基于硬件隔离增强risc-v调试安全2_安全提议

安全之安全(security)博客目录导读

2023 RISC-V中国峰会 安全相关议题汇总 说明:本文参考RISC-V 2023中国峰会如下议题,版权归原作者所有。

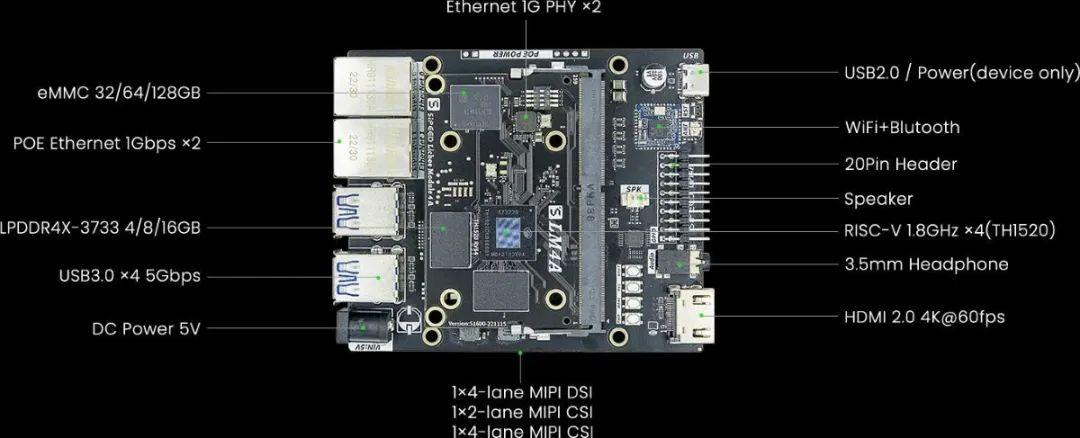

openEuler RISC-V 成功适配 LicheePi 4A 开发板,推动 RISC-V 生态发展

近期,RISC-V SIG 在 LicheePi 4A 开发板上成功实现了欧拉操作系统的适配。目前,最新版本的 openEuler RISC-V 23.03 V1 镜像已在 LicheePi 4A 开发板上可用,这一成果再次展现了 openEuler 在推动 RISC-V 生态发展过程中所取得的新突破。

下载…

搭建qemu RISC-V运行Linux环境

搭建qemu RISC-V运行Linux环境 - 知乎

搭建qemu RISC-V运行Linux环境 1.本文概述 2.工具介绍 2.1 riscv-gnu-toolchain 2.2 spike 2.3 RISC-V Porxy Kernel 2.4 编译工具 3.编译Linux Kernel 4.编译busybox 5.制作根文件系统 6.编译安装qemu 7.启动基本Linux程序 8.运行发行版…

从零学习开发一个RISC-V操作系统(三)丨嵌入式操作系统开发的常用概念和工具

本篇文章的内容 一、嵌入式操作习系统开发的常用概念和工具1.1 本地编译和交叉编译1.2 调试器GDB(The GNU Project Debugger)1.3 QEMU模拟器1.4 项目构造工具Make 本系列是博主参考B站课程学习开发一个RISC-V的操作系统的学习笔记,计划从RISC…

RISC-V Reader 笔记(七)RV64,特权架构,未来可选扩展

RV64

比起 RV32,其实扩展不多。 主要是添加了一系列字,双字为单位的操作。 各个 ISA 32 64比较

x86:变量都存在寄存器里,不像 32 存在内存里,因此指令数少很多,但是因此添加了很多新操作码来操作更多的寄…

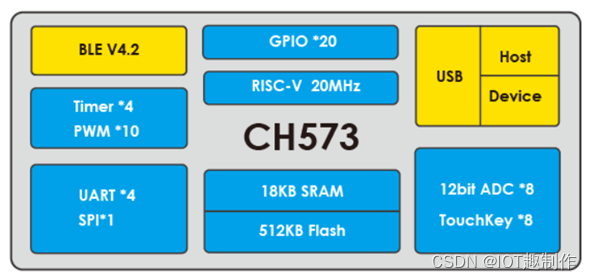

CH573-00-简介——RISC-V内核BLE MCU快速开发教程

一、本系列内容简介 本系列文章为个人在学习并使用CH573这款RISC-V内核BLE MCU的过程中进行的记录总结,以帮助大家快速开发(非深入开发),每节内容对应CSDN的一篇文章,详见主页,完整内容结构如下所示&#x…

说说RISC-V的x0寄存器

RISC-V有32个通用寄存器,其中第1个寄存器x0硬编码为0,即读出来总是0,写进去总是被丢弃。x0为RISC-V指令集的简化可贡献不少啊。

mingdu.zheng at gmail dot com http://blog.csdn.net/zoomdy/article/details/79343785

搞过Linux的都知道Li…

Ubuntu上 RISC-V64 Jemalloc 编译补丁(修复无法链接问题)

它的问题跟这个是相同的;

RISC-V平台 std::atomic<T> 编译失败问题解决-CSDN博客 区别是自己写的代码,能改掉,但是 Jemalloc 编译好的静态库。 比如:我们是在其它平台上面交叉编译的 RISC-V程序࿰…

【全志D1-H 哪吒开发板】Debian系统安装调教和点灯指南

全志D1-H开发板【哪吒】使用Deabian系统入门

特别说明: 因为涉及到操作较多,博文可能会导致格式丢失 其中内容,会根据后续使用做优化调整

目录:

参考资料固件烧录启动调教点灯问题

〇、参考资料 官方资料 开发板-D1开发板【…

在 RISC-V Linux 内核中添加模块

在 RISC-V Linux 内核中添加模块

flyfish

本例以添加helloworld字符设备为例

一 源码配置

1 源码

源码文件helloworld.c拷贝到 drivers/char 目录中 源码主要是输出Hello world init

2 Kconfig

打开drivers/char 目录下的Kconfig文件

在endmenu之前加上

config HELLO…

基于RISC-V架构的通信DSP的设计以及在5G RedCap基带中的应用(五)-基于RISC-V的RedCap DSP在5G基带中的应用

4 基于RISC-V的RedCap DSP在5G基带中的应用

4.1 基带处理器的关键任务和性能需求

基带处理器是移动通信设备中的关键部件,负责处理无线信号,包括信号的接收、发送和处理。在5G通信系统中,基带处理器的关键任务和性能需求包括以下几个方面&a…

Linux 中的 chkconfig 命令及示例

先决条件:Linux 中的运行级别

chkconfig命令用于列出所有可用的服务并查看或更新其运行级别设置。简而言之,它用于列出服务或任何特定服务的当前启动信息,更新服务的运行级别设置以及在管理中添加或删除服务。

概要:

chkconfig --list [名称]

chkconfig --添加名称

chkc…

【RISC-V 指令集】RISC-V DSP 扩展指令集介绍(二)

前言:

本笔记是基于对RISC-V DSP扩展指令集文档总结的,《P-ext-proposal.pdf》文档的关键内容如下: 主要介绍了RISC-V的P扩展指令集及其相关细节。

首先,对P扩展指令进行了概述,并列出了其与其他扩展重复的指令。

…

强化自主可控,润开鸿发布基于RISC-V架构的开源鸿蒙终端新品

2023 RISC-V中国峰会于8月23日至25日在北京召开,峰会以“RISC-V生态共建”为主题,结合当下全球新形势,把握全球新时机,呈现RISC-V全球新观点、新趋势。本次大会邀请了RISC-V国际基金会、业界专家、企业代表及社区伙伴等共同探讨RISC-V发展趋势与机遇,吸引超过百余家业界企业、高…

沁恒微WCH32v003驱动ST7735S硬件spi+DMA调试小坑(2)

上一篇文章解决了spidma传输数据时DC线操作时序不匹配的问题,但是屏幕依旧没有点亮,所以这一篇文章继续找还存在的问题。上一篇文章:沁恒微WCH32v003驱动ST7735S硬件spiDMA调试小坑-CSDN博客 老规矩,先用逻辑分析仪抓取一下波形。…

RISC-V走向开放服务器规范

原文:RISC-V Moving Toward Open Server Specification

作者:Agam Shah

转载自:https://www.hpcwire.com/2023/07/24/risc-v-moving-toward-open-server-specification/

中文翻译:

2023年7月24日

RISC-V International目前正…

程序数据模型由OS还是硬件架构决定?

文章目录 前言硬件架构的作用OS的作用编译器的角色OS的数据模型参考 前言

在文章 1>>32的结果是1还是0 中提到了数据模型 L P 64 LP64 LP64 ,并提出这个数据模型主要是由 U n i x Unix Unix 以及类 U n i x Unix Unix 的操作系统使用居多,例如…

通过RISC-V预认证解决方案应对功能安全挑战

安全之安全(security)博客目录导读

2023 RISC-V中国峰会 安全相关议题汇总 说明:本文参考RISC-V 2023中国峰会如下议题,版权归原作者所有。

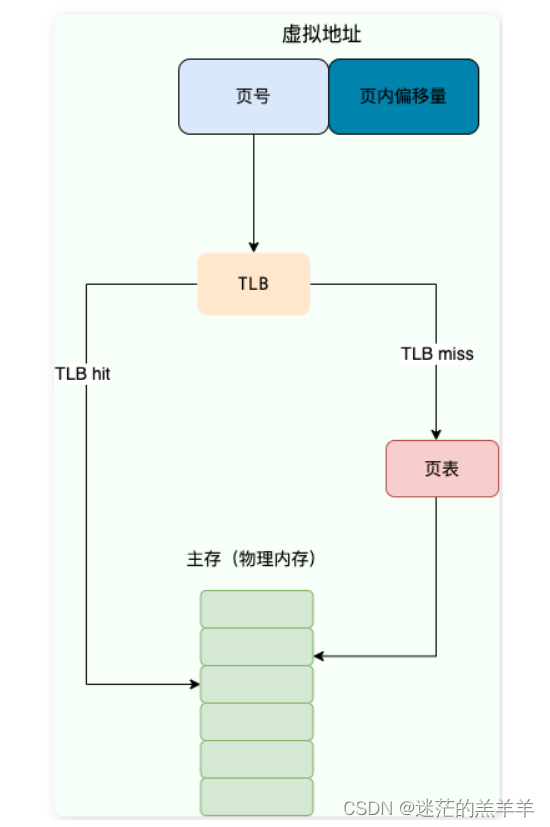

操作系统——内存管理(附带Leetcode算法题LRU)

1.内存管理主要用来干什么?

操作系统的内存管理主要负责内存的分配与回收、内存扩充(虚拟技术)、地址转换(逻辑-物理)、内存保护(保证各进程在自己的内存空间运行,不会越界访问).....

2.什么是内存碎片?

内存碎片是内存的申请和释放产生的…

AG32 MCU 如何进入低功耗模式

默认情况下,微控制器(MCU)在系统复位或电源复位后处于运行模式。当CPU不需要持续运行时,可以使用几种低功耗模式来节省功耗。这是由用户选择的模式,给出了低功耗,短启动时间和可用的唤醒源之间的最佳妥协。 AG32VF 系列MCU具有以下…

[RISCV] 发现一个可以看RISC-V CPU行为的开源项目

最近在浏览某大型程序员交友 网站的时候发现一个好玩的项目,介绍如下: A small program that handles mie, msi, mti and trap interrupts and updates some global variables on interrupts. 重点是他下面还放了一张图: 能看到RISCV CSR的行为太酷啦!!!

下面一起setup一…

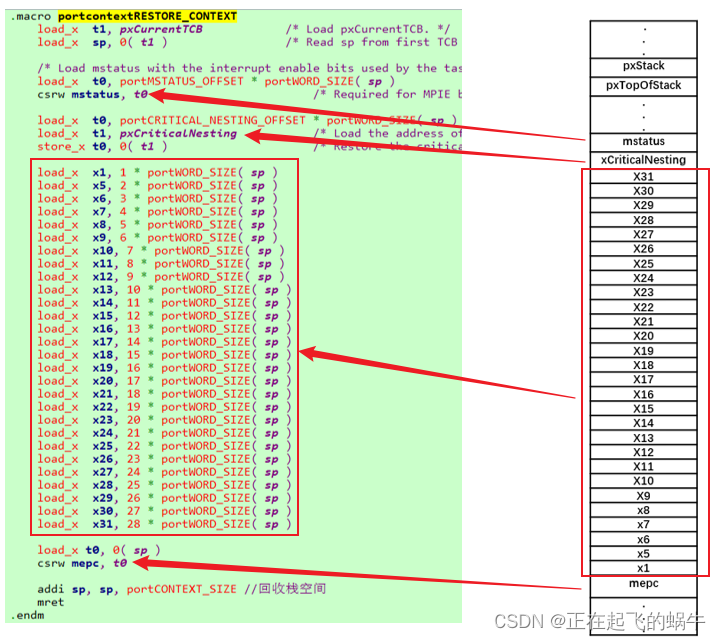

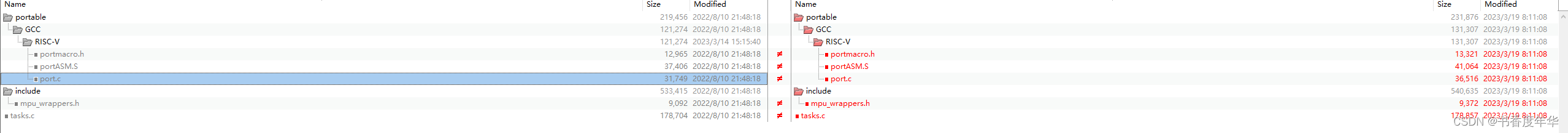

freertos任务切换的现场保存、恢复(任务栈空间)深度分析(以RISC-V架构为例)

1、任务控制块在内存中的布局 RISC-V架构采用的减栈,即栈向低地址空间生长;在freertos中采用任务控制块(TCB)结构来表示一个任务每个任务有自己的任务栈,任务栈是紧挨着TCB的,且TCB在地址高位,任…

使用 C++23 从零实现 RISC-V 模拟器

使用 C23 从零实现 RISC-V 模拟器

使用 C23 从零实现的 RISC-V 模拟器,最终的模拟器可以运行 xv6 操作系统。

教程: everystep代码: crvemu

本教程参考了 Asami 所写的 Rust 版本的模拟器教程 ,但是原版只写了前三章。此外也参考了 Rare 对 rvemu 的改…

韦东山D1S板子——利用xfel工具初始化内置64MB内存,并直接下载程序到内存运行

1、前言 (1)最近使用韦东山老师的D1S板子学习RISC-V架构知识,我是结合《RISC-V体系结构编程与实践》这本书的进行学习,其中韦东山老师对书中的代码做了部分移植,到MMU模块就没有在移植书中代码; ࿰…

6.1810: Operating System Engineering Lab: Xv6 and Unix utilities By:Haostart

前言

开学后要为一年后找实习做准备了,准备打一下基础,就做一下MIT-6.S081,是2022版的,地址如下 6.1810: Operating System Engineering Lab

Lab

做实验前一定要清楚Xv6的系统调用有哪些!!! 做实验前一定要清楚Xv6的系统调用有哪些!!!

1. sleep

由于系统调用里已经有slee…

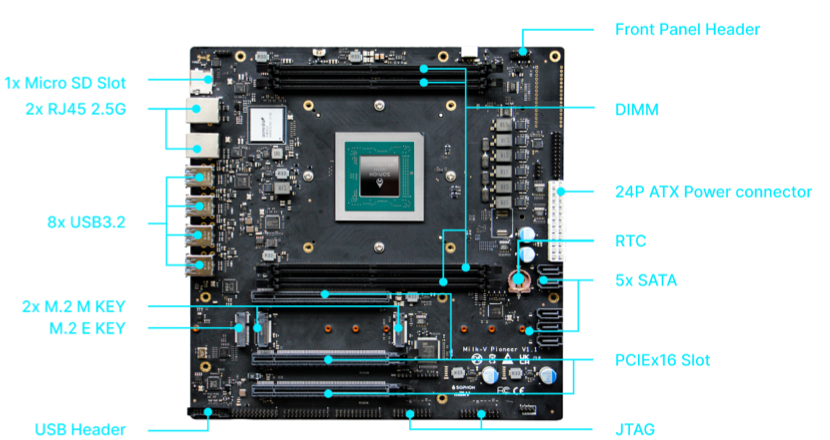

Lichee Pi 4A:RISC-V架构的开源硬件之旅

一、简介 Lichee Pi 4A是一款基于RISC-V指令集的强大Linux开发板,它凭借出色的性能和丰富的接口,吸引了众多开发者和爱好者的关注。这款开发板不仅适用于学习和研究RISC-V架构,还可以作为软路由、小型服务器或物联网设备的核心组件。 目录

一…

平头哥玄铁系列 RISC-V 芯片及开发板

1、玄铁 9 系列概述

玄铁 8 系列 基于C-SKY架构,玄铁 9 系列基于 RISC-V 架构。E 系列为 RISC-V 32 位,C 系列为 RISC-V 64 位。 E902:超低功耗 RSIC-V 架构处理器 E902 采用 2 级极简流水线兼容 RISC-V 架构且对执行效率等方面进行了增强&a…

【全网唯一】 自己动手实现 FreeRTOS-metal-SU

前言 FreeRTOS 是一个开源的实时操作系统(RTOS),适用于微控制器和小型嵌入式系统。它提供了多任务处理、内存管理、定时器、软件定时器、消息队列和信号量等功能,以帮助开发人员构建可靠和高效的嵌入式系统。

FreeRTOS 的设计原则…

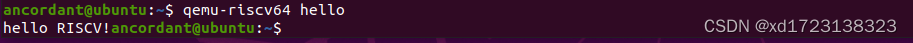

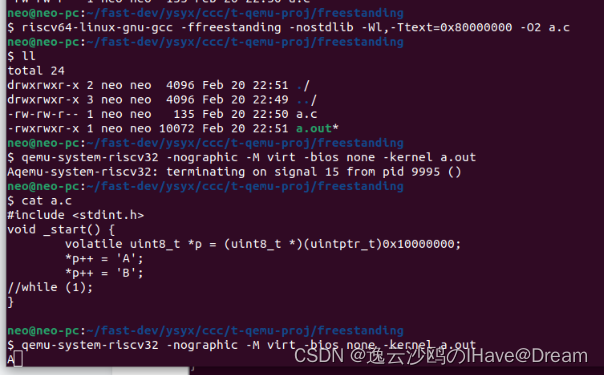

【riscv】使用qemu运行riscv裸机freestanding程序

文章目录 1. 运行显示2. 工具准备3. 裸机代码和编译3.1 源码3.2 编译 4. 使用qemu仿真运行riscv裸机程序 1. 运行显示

详见左下角, 运行时串口输出的字符 A ;

2. 工具准备

# for riscv64-linux-gnu-gcc

sudo apt-get install gcc-riscv64-linux-gnu# for qemu-s…

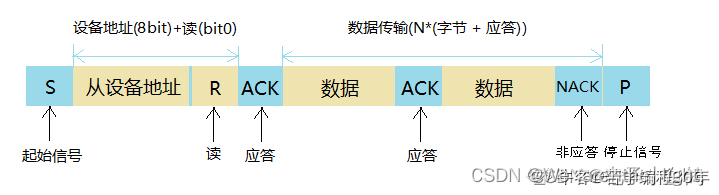

[RISC-V]Milk-V开发板 i2c测试oled及波形输出

I2C3

引脚图 修改i2c3复用功能

build\boards\cv180x\cv1800b_sophpi_duo_sd\u-boot\cvi_board_init.c

//I2C3 pin6 7

PINMUX_CONFIG(SD1_CMD, IIC3_SCL);

PINMUX_CONFIG(SD1_CLK, IIC3_SDA);扫描I2C3上的设备

[rootcvitek]~# i2cdetect -y -r 3 0 1 2 3 4 5 6 7 8 9 a b c …

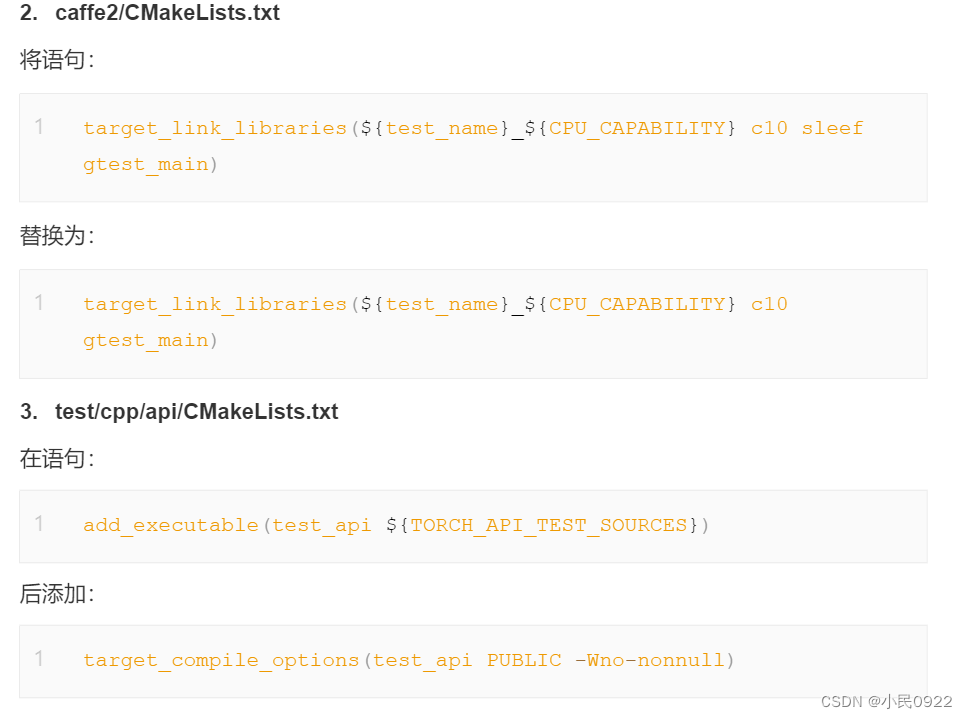

risc-v编译飞浆

git submodule update --init --recursive报错 根据算能RISC-V通用云编译飞桨paddlepaddleopenKylin留档_在riscv下进行paddlelite源码编译-CSDN博客

(torch2-2) rootlpi4a:/home/sipeed/Desktop/paddle/third_party# git submodule update --init --recursive fatal: detecte…

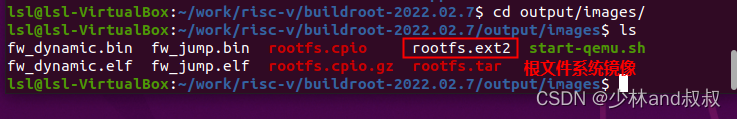

基于QEMU的RISC-V架构linux系统开发(三)——基于buildroot的最小根文件系统配置与编译

1.buildroot官网下载最新版本的buildroot。

https://buildroot.org/download.html 图1 下载最新版本的buildroot压缩包 2.拷贝buildroot软件包到工作目录,并解压buildroot。 图2 解压buildroot软件包 3.新建编译脚本build_risc-v.sh,使用buildroot自带的…

RISC-V公测平台发布 · 在SG2042上配置Jupiter+Octave科学计算环境

简介

JupyterHub是一个开源的共享计算平台,它为每个用户管理一个单独的 Jupyter 环境, 可以用于学生班级、企业数据科学小组或科学研究小组。它是一个多用户中心,可以生成、管理和代理多个单用户Jupyter笔记本服务器的实例。

GNU Octave是一…

如何学习RISC-V

学习RISC-V可以按照以下步骤进行:

学习基础知识。了解计算机系统的基础知识,包括计算机组成、汇编语言、操作系统等。这可以帮助你更好地理解RISC-V指令集架构的基础知识。学习RISC-V指令集架构。RISC-V是一种基于精简指令集(RISC࿰…

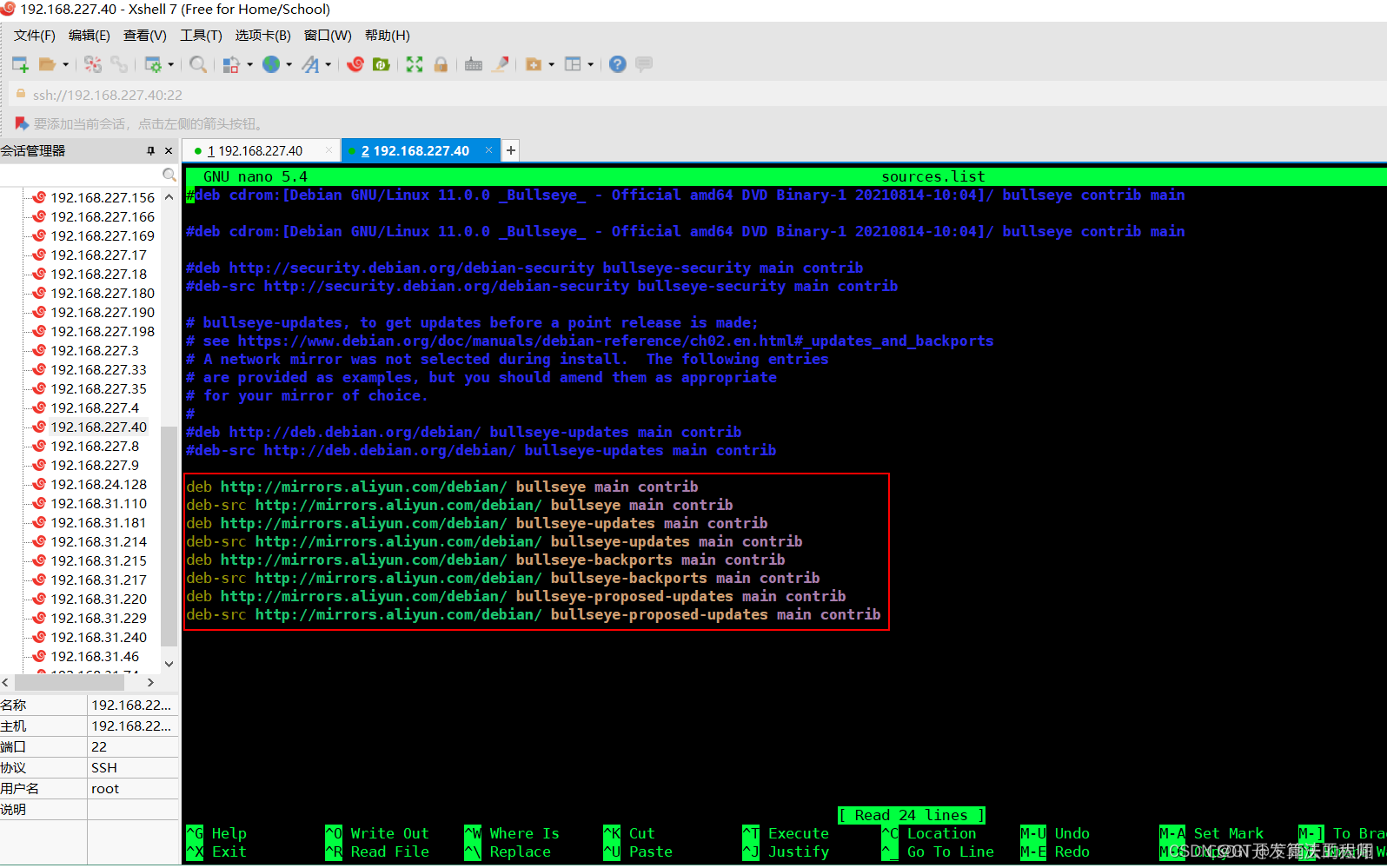

M1-ARM64-RISCV64 编译工具链(milkv-duo或Xuantie-900指令构架可用)

本工具链在虚拟机Parallels - Debian 11.7 - ARM64 系统下编译/验证通过

已存放百度网盘, 包含打包后的img镜像文件 链接: https://pan.baidu.com/s/1K9RVYnv8Wc3Ln8yc0oxwdg 提取码: 9255

1. Debian 11.7 ARM 版本系统下载,也可在ARM64真机操作

https://mirror.…

沁恒 CH32V208(二): CH32V208的储存结构, 启动模式和时钟

目录

沁恒 CH32V208(一): CH32V208WBU6 评估板上手报告和Win10环境配置沁恒 CH32V208(二): CH32V208的储存结构, 启动模式和时钟

CH32V 存储容量命名方式

在介绍下面的内容前, 先看一下CH32V系列和存储相关的命名格式, 以CH32V203为例, 前面的CH32V203代表一个系列, 后面的字…

算能RISC-V通用云开发空间openKylin留档

终于可以体验下risc-v了! 操作系统是openKylin,算能的云空间 尝试编译安装pytorch

首先安装git

apt install git

然后下载pytorch和算能cpu的库:

git clone https://github.com/sophgo/cpuinfo.git

git clone https://github.com/pytorc…

算能RISC-V通用云开发空间编译pytorch @openKylin留档

终于可以体验下risc-v了! 操作系统是openKylin,算能的云空间 尝试编译安装pytorch

首先安装git

apt install git

然后下载pytorch和算能cpu的库:

git clone https://github.com/sophgo/cpuinfo.git

git clone https://github.com/pytorc…

RISC-V和ARM

参考:https://www.eet-china.com/mp/a39867.html

RISC-V和ARM都是基于**精简指令集计算 (RISC)**原理建立的指令集架构。他们的主要区别在于他们的授权模式和开放性:

ARM 是一种专有的指令集架构,众多使用ARM架构的厂商,只能根据…

QEMU 仿真RISC-V freeRTOS 程序

1. 安裝RISC-V 仿真環境 --QEMU

安裝包下載地址: https://www.qemu.org/

安裝命令及安裝成功效果如下所示,

target-list 設定爲riscv32-softmmu,

$ cat ~/project/qemu-8.0.4/install.sh

sudo apt-get install libglib2.0-dev

sudo apt-get install libpixman-1-dev

./co…

openEuler RISC-V 23.03 创新版本亮相:全面提升硬件兼容性和桌面体验

近日,openEuler RISC-V 23.03 创新版本正式发布。openEuler RISC-V SIG 作为 openEuler 系统在 RISC-V 架构上的维护组织,主要致力于 openEuler 在 RISC-V 软硬件方面的适配,一直跟随 openEuler 版本节奏提供 openEuler 的 RISC-V 镜像版本。…

串行通信——IIC总结

一.什么是IIC?

IIC(Inter-Integrated Circuit)也称I2C,中文叫集成电路总线。是一个多主从的串行总线,由飞利浦公司发明的通讯总线,属于半双工同步传输类总线,仅由两条线就能完成多机通讯&#…

【萌新的RiscV学习之流水线结构的概述-7】

萌新的RiscV学习之流水线结构的概述-7

之前写完了单周期的指令 目前朝着流水线迈进 由于涉及学业机密 就不展示代码了 主要展示学习过程和一些想法 由于时钟周期必须满足所有指令中最坏的情况,所以不能使用那些缩短常用指令执行时间而不改变最坏情况的实现技术。因…

RISC-V 使用位域

RISC-V 使用位域

MISRA C 不建议使用位域,因为 C 标准没有定义位域的排列方式。但是,只要能确定位域的排列方式,还是可以使用。

RISC-V 的位域:低位在先。

如果编译器足够聪明,那么使用位域和位宏应该产生一样的代码…

【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(十)- 向量整数算术指令

1. 引言

以下是《riscv-v-spec-1.0.pdf》文档的关键内容: 这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量…

【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(九)- 向量定点算术指令

1. 引言

以下是《riscv-v-spec-1.0.pdf》文档的关键内容: 这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量…

[伴学笔记]01-操作系统概述 [南京大学2024操作系统]

文章目录 前言jyy:01-操作系统概述 [南京大学2024操作系统]为什么要学操作系统?学习操作系统能得到什么? 什么是操作系统?想要明白什么是操作系统:时间线:1940s1950s-1960s1960-1970s年代. 信息来源: 前言 督促自己,同时分享所得,阅读完本篇大约需要10分钟,希望为朋友的技术…

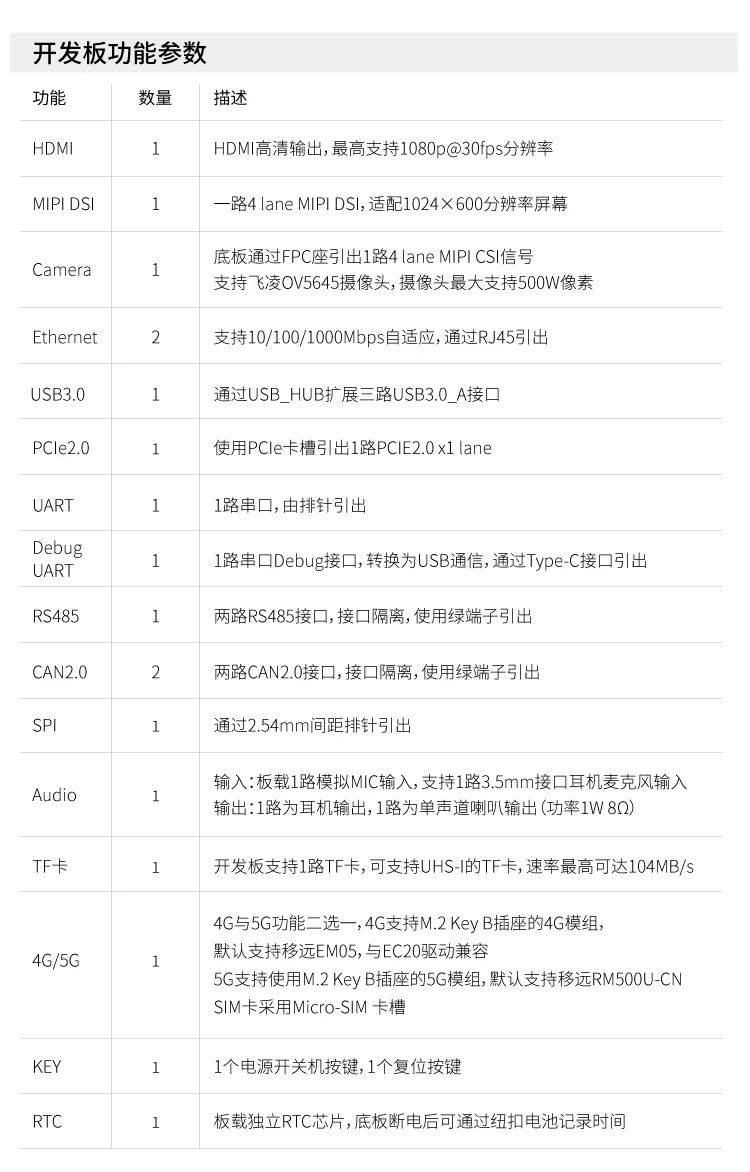

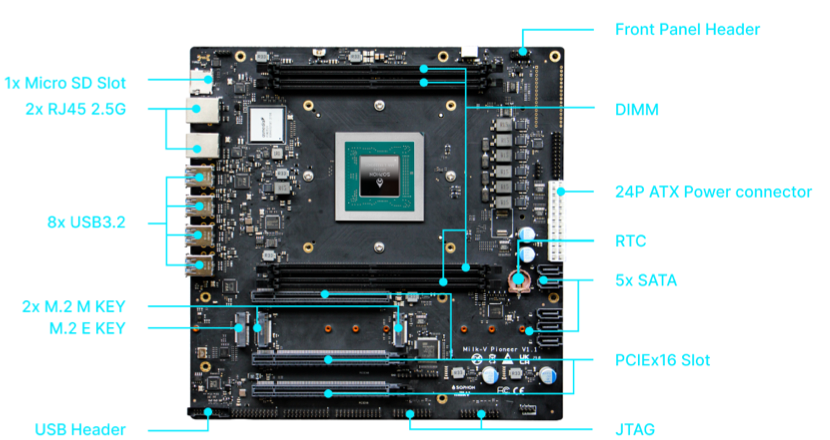

RISC-V架构 | 飞凌嵌入式FET7110-C国产高性能核心板现货发售!

RISC-V凭借其完全开源免费且可自由修改的特性而备受国内厂商的追捧,在此背景下,飞凌嵌入式联合RISC-V国产处理器厂商赛昉科技(StarFive)基于昉惊鸿7110处理器共同推出FET7110-C核心板。

现在,飞凌嵌入式FET7110-C核心板(商业级&a…

freerots启动过程分析(qemu仿真RISC-V架构为例)

1、前言

本文是基于qemu上virt板子适配的freertos系统源码进行讲解qemu安装可参考博客:《qemu源码下载和安装》;freertos移植到qemu上运行可参考博客:《移植freertos到qemu上运行》;

2、汇编代码部分 汇编文件:FreeR…

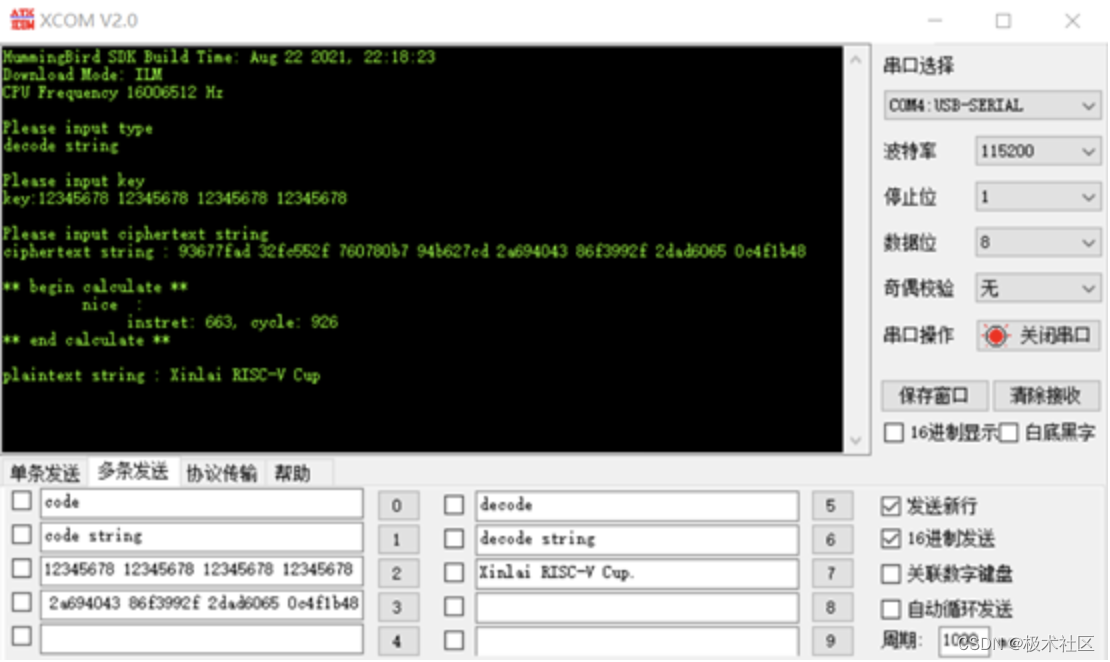

【2021集创赛】 RISC-V杯三等奖:基于E203 处理器的SM4算法硬件加速

杯赛题目:基于蜂鸟E203 RISC-V处理器内核的SoC设计 参赛要求:研究生组/本科生组 赛题内容: 基于芯来科技的开源蜂鸟E203 Demo SoC进行扩展,在限定的可编程逻辑平台上构建面向专用应用领域(譬如人工智能、信息安全、工业…

RISC-V单板计算机模拟和FPGA板多核IP实现

🎯要点

🎯使用单板计算机 Visionfive 2 或模拟器测试RISC-V汇编🎯RISC-V汇编加载和算术。🎯使用GNU MAKE汇编RISC-V指令,ESP32使用CMake编译执行指令。🎯RISC-V汇编功能和使用释义:控制指令&am…

5. Linux-riscv内存管理21-24问

文章目录 2.5 在中断上下文中能不能调用包含GFP_KERNEL分配掩码的内存分配函数?2.5.1 zone水位2.5.2 GFP_ATOMIC2.5.3 在使用GPF_KERNEL情况下,什么时候才睡眠?2.5 在中断上下文中能不能调用包含GFP_KERNEL分配掩码的内存分配函数?

在中断上下文中不能使用包含GFP_KERNEL分…

【操作系统xv6】学习记录5--实验1 Lab: Xv6 and Unix utilities

ref:https://pdos.csail.mit.edu/6.828/2020/xv6.html 实验:Lab: Xv6 and Unix utilities

环境搭建

实验环境搭建:https://blog.csdn.net/qq_45512097/article/details/126741793 搭建了1天,大家自求多福吧,哎。~搞环境真是折磨…

Imagination:RISC-V CPU的重要力量

根据SHD集团最近发布的报告显示,RISC-V正全速发展中。通过分析从2021年到2030年这十年间RISC-V核在不同应用和功能领域的潜在市场,作者Rich Wawrzyniak得出结论称,到2030年,22.3%的SoC将包含RISC-V CPU,RISC-V的收入预…

RISC-V/ARM mcu OpenOCD 调试架构解析

Risc-v/ARM mcu OpenOCD 调试架构解析

最近有使用到risc-v的单片机,所以了解了下risc-v单片机的编译与调试环境的搭建,面试时问到risc-v的调试可参看以下内容。

risc-v根据官方的推荐,调试器服务是选择OpenOCD,DopenOCD(开放片上…

xv6项目开源—04

xv6项目开源—04

理论

本章讲的是陷阱指令和系统调用

1)有三种事件会导致中央处理器搁置普通指令的执行,并强制将控制权转移到处理该事件的特殊代码上:

系统调用、异常、设备中断

2)Xv6陷阱处理分为四个阶段: RIS…

基于openKylin与RISC-V的MindSpore AI项目实践

项目目标: 在openKylin系统上安装和配置MindSpore框架。开发一个简单的图像分类模型,并在RISC-V平台上进行训练和推理。根据RISC-V的特性,对MindSpore框架进行必要的优化。 目录

项目目标:

训练模型

编写训练代码,设…

学习开发一个RISC-V上的操作系统(汪辰老师) — 一次RV32I加法指令的反汇编

前言 (1)此系列文章是跟着汪辰老师的RISC-V课程所记录的学习笔记。 (2)该课程相关代码gitee链接; (3)PLCT实验室实习生长期招聘:招聘信息链接 前置知识

RISC-V 汇编指令编码格式 &a…

【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(二)-向量元素到向量寄存器状态的映射

1. 引言

以下是《riscv-v-spec-1.0.pdf》文档的关键内容: 这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量…

【开源鸿蒙】编译OpenHarmony轻量系统QEMU RISC-V版

文章目录 一、背景介绍二、准备OpenHarmony源代码三、准备hb命令3.1 安装hb命令3.2 检查hb命令 四、编译RISC-V架构的OpenHarmony轻量系统4.1 设置hb构建目标4.2 启动hb构建过程 五、问题解决5.1 hb set 报错问题解决 六、参考链接 开源鸿蒙坚果派,学习鸿蒙一起来&a…

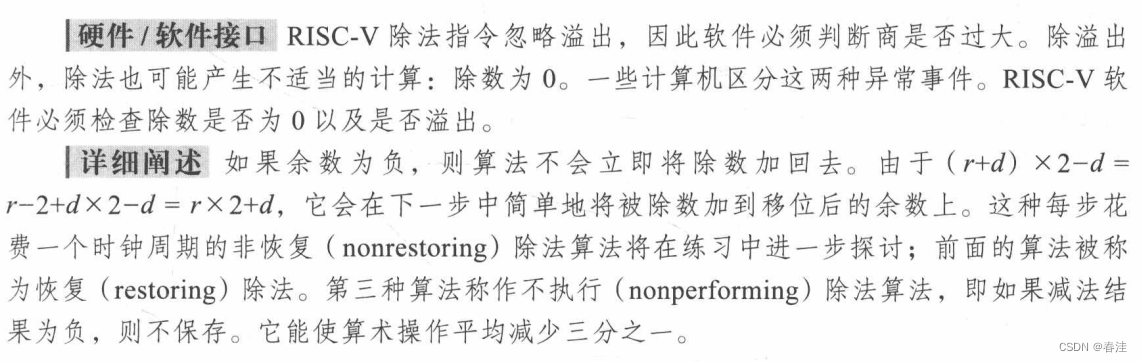

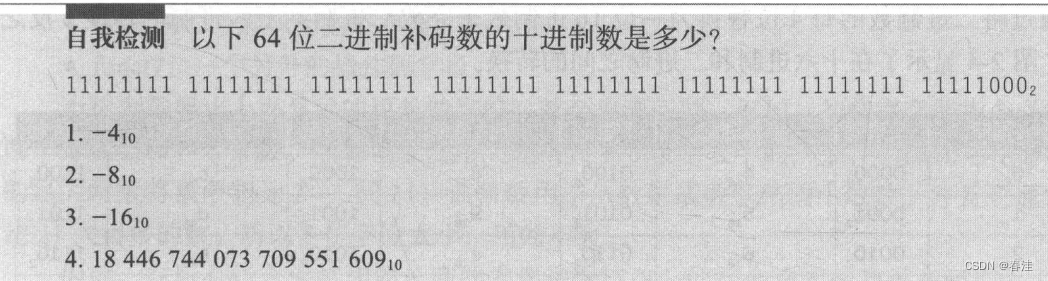

读书·计算机组成与设计:软硬件接口RISC-V版·第三章

加法和减法 减法: 将负数用二进制补码的形式表现出来并相加

补码: 除了符号位,其他位置 取反 1

正数 👉 负数补码: 全部取反 1

负数补码 👉 正数 : 全部取反 1

减法就是: 将 相…

RISC-V体系结构的U-Boot引导过程 第一阶段

RISC-V体系结构的U-Boot引导过程 第一阶段

flyfish

.globl _start

_start:.globl使符号对链接器可见相当于C语言中的Extern,声明此变量,并且告诉链接器此变量是全局变量,外部可以访问.u-boot.lds里的ENTRY(_start)也是这里的_start。 即指定…

RISV-V架构的寄存器介绍

1、RISC-V的通用寄存器 (1)在编写汇编代码时,使用寄存器的ABI名字,一般不直接使用寄存器的编号; (2)x0-x31是用来做整形运算的寄存器,f0-f31是用来做浮点数运算的寄存器;…

沁恒 CH32V203C8T6 RISC-V 单片机无法烧写

单片机:CH32V203C8T6 IDE: MounRiver Studio v1.90 单片机架构:RISC-V 问题描述: 新打回来的板子,无法烧写程序,提示如下: ------------ Begin flash process of "obj\TR350.hex" ---…

从零学习开发一个RISC-V操作系统(一)丨计算机组成原理相关知识与RISC-V指令集简介

本篇文章的内容 一、计算机组成原理的相关知识1.1 计算机的硬件组成1.2 程序的存储与执行1.3 程序语言的设计和进化1.4 存储设备的层次结构1.5 操作系统 二、RISC-V的指令集ISA简介2.1 什么是ISA2.2 复杂指令集(CISC)和精简指令集(RISC&#…

CH8571 沁恒微 RISC-V EC 用芯片实验 (一)参考手册 第一章 接脚描述

CH8571 沁恒微 RISC-V EC 用芯片实验 (一)参考手册 第一章 接脚描述 源起基础规格Features 芯片特性RISC-V嵌入式控制器eSPI Interface接口LPC接口嵌入式闪存EC时钟源SMBus Interface 接口系统唤醒控制EC唤醒控制中断控制器定时器/看门狗定时器UARTACPI 电源管理通道BRAMGPIO…

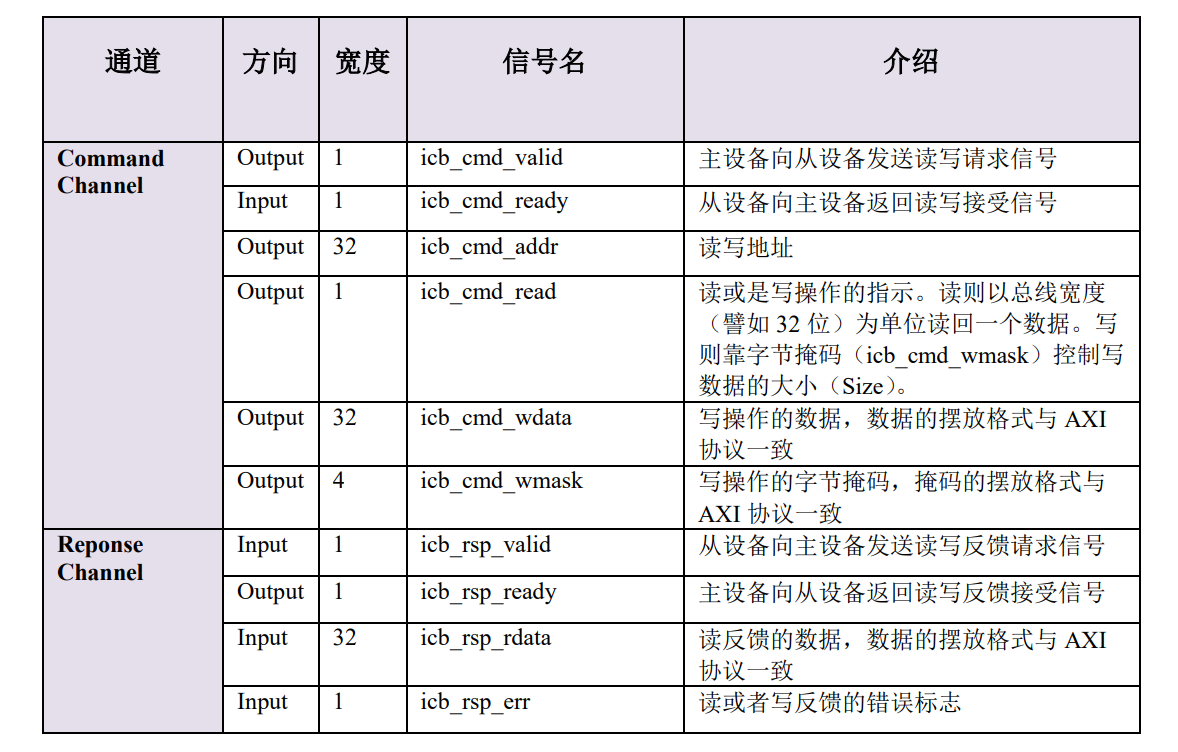

SOC总线学习记录之ICB(Internal Chip Bus)

蜂鸟E203总线:

采用自定义总线协议 ICB(Internal Chip Bus),该总线用于蜂鸟 E203 内核内部使用,同时也可作为 SoC 中的总线使用。 ICB 总线的初衷是为了能够尽可能地结合 AXI 总线和 AHB 总线的优点,兼具高…

沁恒 CH32V208(五): CH32V208 运行FreeRTOS示例的说明

目录

沁恒 CH32V208(一): CH32V208WBU6 评估板上手报告和Win10环境配置沁恒 CH32V208(二): CH32V208的储存结构, 启动模式和时钟沁恒 CH32V208(三): CH32V208 Ubuntu22.04 Makefile VSCode环境配置沁恒 CH32V208(四): CH32V208 网络DHCP示例代码分析沁恒 CH32V208(五): CH32V2…

DatenLord前沿技术分享 No.36

达坦科技专注于打造新一代开源跨云存储平台DatenLord,通过软硬件深度融合的方式打通云云壁垒,致力于解决多云架构、多数据中心场景下异构存储、数据统一管理需求等问题,以满足不同行业客户对海量数据跨云、跨数据中心高性能访问的需求。在本周…

学习开发一个RISC-V上的操作系统(汪辰老师) — unrecognized opcode `csrr t0,mhartid‘报错问题

前言 (1)此系列文章是跟着汪辰老师的RISC-V课程所记录的学习笔记。 (2)该课程相关代码gitee链接; (3)PLCT实验室实习生长期招聘:招聘信息链接 正文 (1)在跟着…

TinyEMU源码分析之虚拟机初始化

TinyEMU源码分析之虚拟机初始化 1 初始化结构参数2 配置RAM地址空间3 初始化设备4 拷贝BIOS和Kernel5 手动写入5条指令6 体验第一条指令的执行 本文属于《

TinyEMU模拟器基础系列教程》之一,欢迎查看其它文章。 本文中使用的代码,均为伪代码,…

MIT 6.S081---Lab: locks

Memory allocator (moderate)

修改kernel/kalloc.c,修改kmem声明并定义结构体数组: 修改kernel/kalloc.c中的kinit函数,对kmemList进行初始化: 修改kernel/kalloc.c中的kfree函数,获取当前的cpuid并将释放的内存添加到…

RISC-V Optimization Guide(笔记)

官网发表的文章地址:RISC-V Optimization Guide B站有人做过解读视频,这篇文章也是看视频时做的笔记:视频地址

一、标量整数优化

1.1 常量的具体化

使用lui/addiw将立即数加载至寄存器,当立即数低12位的最高位为1时,…

【开源鸿蒙】使用QEMU运行OpenHarmony轻量系统

文章目录 一、准备工作1.1 编译输出目录简介 二、QEMU安装2.1 安装依赖2.2 获取源码2.3 编译安装2.4 问题解决 三、用QEMU运行OpenHarmony轻量系统3.1 qemu-run脚本简介3.2 qemu-run脚本参数3.3 qemu-run运行效果3.4 退出QEMU交互模式 四、问题解决五、参考链接 开源鸿蒙坚果派…

MIT 6s081 lab1:Xv6 and Unix utilities

Lab1: Xv6 and Unix utilities

作业网址:https://pdos.csail.mit.edu/6.828/2020/labs/util.html

Boot xv6(easy)

下载,启动xv6系统

$ git clone git://g.csail.mit.edu/xv6-labs-2020

Cloning into xv6-labs-2020...

...

$ cd xv6-labs-2020

$ git …

【【萌新的RiscV学习之流水线控制-9】】

萌新的RiscV学习之流水线控制-9

我们按照在之前的单周期设计加入控制单元 那么我们能够在后续的设计中提供方便 我们也在流水线中加入一个control单元 我们先按照书上的指令op码值介绍一遍基本功能 接下来我们讲述control 的 控制效果 关于这些串口判别的使用 由于控制线从…

龙蜥白皮书精选:开源 RISC-V 技术支持软硬件全栈平台

文/RISC-V ARCH SIG

01 背景介绍

RISC-V 是一套开源指令集为拥抱更加开放的芯片生态,指令集标准和扩展标准采用全球共享共治的模式,于 Arm 和 x86 有很大不同,因此也受到了业内人士的普遍关注,再未来有着很大应用潜力。龙蜥社区…

MIT 6.S081 (BOOK-RISCV-REV1)教材第四章内容 -- Trap -- 下

MIT 6.S081 教材第四章内容 -- Trap -- 下 引言从内核空间陷入页面错误异常Page Fault BasicsLazy page allocationZero Fill On DemandCopy On Write ForkDemand PagingMemory Mapped Files 真实世界 引言

MIT 6.S081 2020 操作系统

本文为MIT 6.S081课程第四章教材内容翻译…

RISC-V 整型通用寄存器介绍

简介

RISC-V64位/32位提供了32个整型通用寄存器,编号是x0~x31,这些整型通用寄存器的宽度与架构位数一致。

浮点数寄存器与整形寄存器一样也提供了32个:f0~f31,位数与架构位数一致。

通用寄存器介绍

零寄存器

x0/zero

x0寄存…

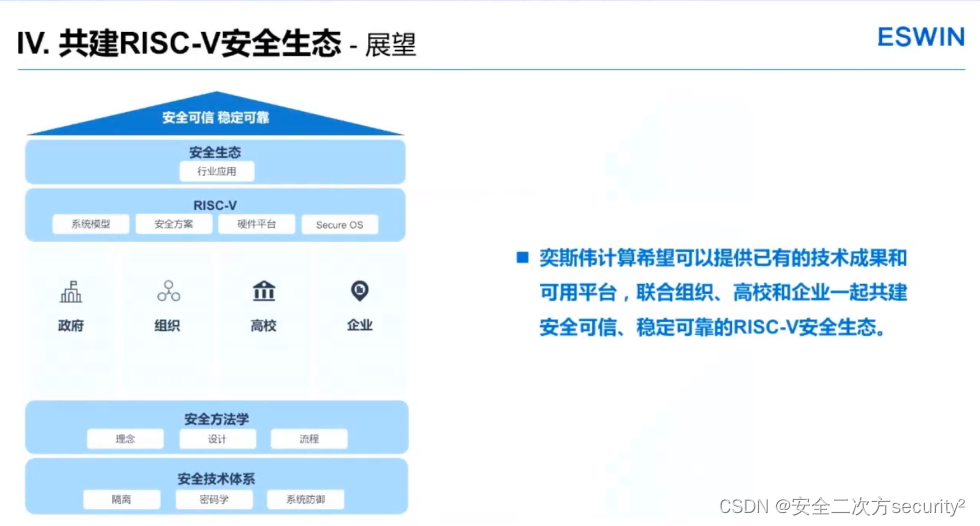

构建安全可信、稳定可靠的RISC-V安全体系

安全之安全(security)博客目录导读

2023 RISC-V中国峰会 安全相关议题汇总 说明:本文参考RISC-V 2023中国峰会如下议题,版权归原作者所有。

RISC-V_WCH系列微控器软件体系云端快速架构

1 概述

RISC-V内核的微控器MCU,正在以更高的性价比,快速取代传统的各类ARM系列微控制处理器。

针对常用的芯成RISC-V内核的泌恒WCH系列微控器MCU,推出了:RISC-V_WCH系列微控器软件体系快速架构云平台。只要以身份证号码做用户名…

12nm工艺,2.5GHz频率,低功耗Cortex-A72处理器培训

“ 12nm工艺,2.5GHz频率,低功耗Cortex-A72处理器培训”

本项目是真实项目实战培训,低功耗UPF设计,后端参数如下:

工艺:12nm

频率:2.5GHz

资源:2000_0000 instances 为了满足更多…

第六十一回 放冷箭燕青救主 劫法场石秀跳楼-编译安装飞桨paddlepaddle@openKylin+RISCV

卢俊义在水里被张顺抓住,用轿子抬到了梁山。宋江等人下马跪在地上迎接,请他坐第一把交椅。卢俊义宁死不从,大家只好说留他在山寨几天,先让李固带着马车货物回去。吴用对李固说,你的主人已经答应坐第二把交椅了…

经纬恒润AUTOSAR产品成功适配芯来RISC-V车规内核

近日,经纬恒润AUTOSAR基础软件产品INTEWORK-EAS(ECU AUTOSAR Software,以下简称EAS)在芯来提供的HP060开发板上成功适配芯来科技的RISC-V处理器NA内核,双方携手打造了具备灵活、可靠、高性能、强安全性的解决方案。这极…

Rust练手:从零手撸RISC-V架构虚拟机(一)(附完整代码)

CPU构成 & 功能

组成计算机的五个经典部件是:输入、输出、存储器、运算器和控制器(合并一块儿称CPU)。

CPU的组成部件为:

运算器:进行数据运算,最处的运算器只有ALU指令控制器:指令解析,控制运算器运…

RISC-V公测平台发布 · 使用YCSB测试SG2042上的MySQL性能

实验介绍:

YCSB(全称为Yahoo! Cloud Serving Benchmark),该性能测试工具由Java语言编写(在之前的MC文章中也提到过这个,如果没看过的读者可以去看看之前MC那一期),主要用于云端或者…

在DongshanPI-D1开箱使用分享与折腾记录实现MPU6050数据读取

前言

上一篇文章使用RT-Smart的IIC驱动OLED屏幕,进行基本的字符串显示,在使用过程中对RT-Smart有了一定熟悉,准备使用SPI驱动ST7789,但SPI接口没有引出,本次使用手上已有的传感器MPU6050进行使用。

过程

本次直接开始添加离线包…

【openeuler】openEuler kernel 技术分享 - 第2期 - 从ARM和RISC-V架构看体系结构对Linux操作

openEuler kernel 技术分享 - 第2期 - 从ARM和RISC-V架构看体系结构对Linux操作系统的支持_哔哩哔哩_bilibili The RISC-V Reader: An Open Architecture Atlas

http://riscvbook.com/chinese/RISC-V-Reader-Chinese-v2p1.pdf

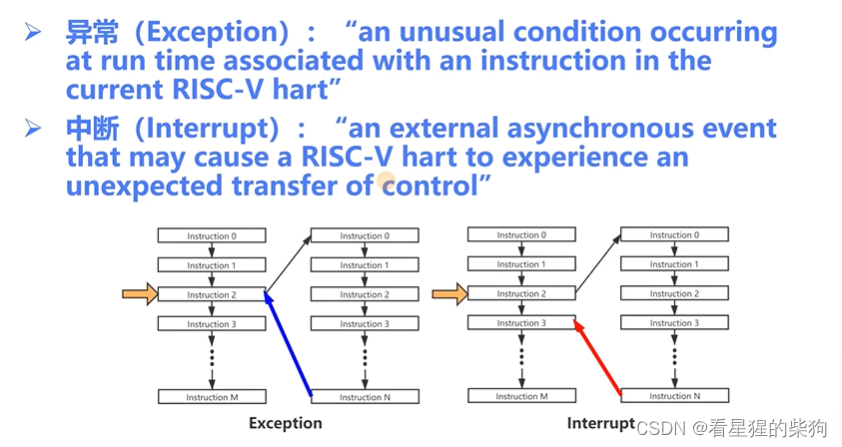

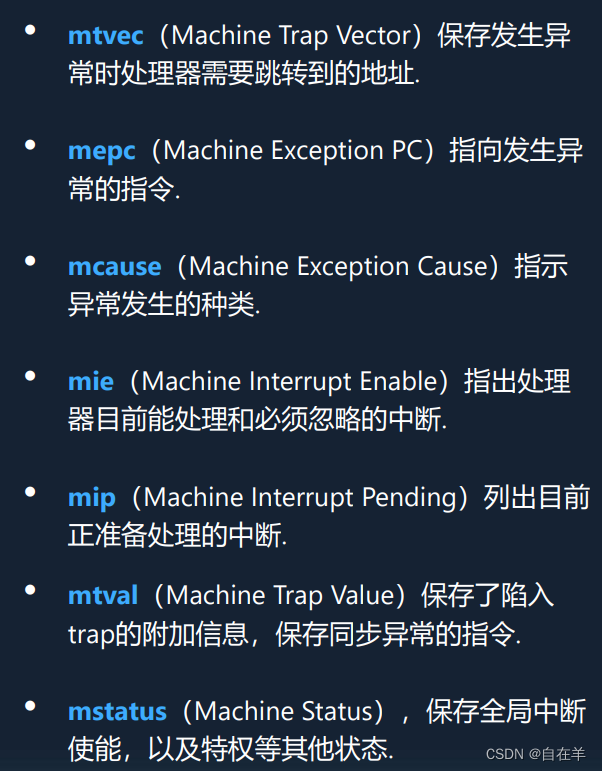

开发一个RISC-V上的操作系统(六)—— 中断(interrupt)和异常(exception)

目录 往期文章传送门

一、控制流 (Control Flow)和 Trap

二、Exceptions, Traps, and Interrupts

Contained Trap

Requested Trap

Invisible Trap

Fatal Trap

异常和中断的异同

三、RISC-V的异常处理

mtvec(Machine Trap-Vector Ba…

RISCV汇编与Linux内核传参

在全志RISCV/D1设备上安装汇编器和链接器

去年笔者将openwrt-22.03系统移植到了基于全志D1/riscv64的嵌入式设备上。当时发现系统启动后,网络不可用;简单地修改/etc/config/network设备即可以正常连接有线网络。为了学习riscv ISA,笔者手动为…

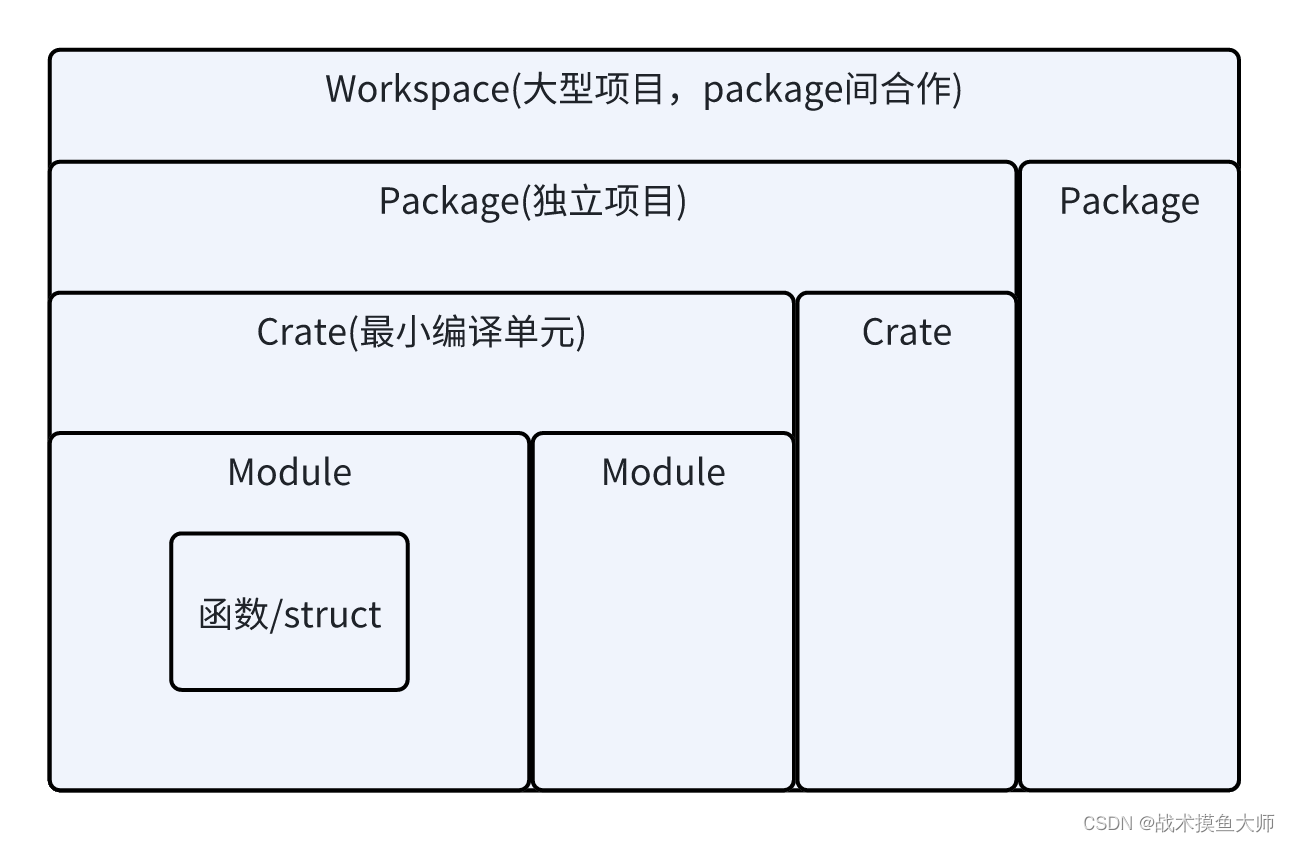

Rust编程(四)PackageCrateModule

这一部分的中文教程/文档都很混乱,翻译也五花八门,所以我建议直接看英文官方文档,对于一些名词不要进行翻译,翻译只会让事情更混乱,本篇从实战和实际需求出发,讲解几个名称的关系。 Module & Crate & Package & Workspace 英文中的意思: Cargo:货物 Crate:…

【学一点RISC-V】RISC-V IMSIC

IMSIC RISC-V AIA 文档 第三章 Incoming MSI Controller (IMSIC) 传入 MSI 控制器(IMSIC)是一个可选的 RISC-V 硬件组件,与 hart 紧密相连,每个 hart 有一个 IMSIC。IMSIC 接收并记录 Hart 的传入消息信号中断 (MSI),并…

ROBdispatch stage

ROB会跟踪所有pipeline中的指令的状态;一旦ROB中,header指的entry complete了,则该指令可以commit,其architectural state属于visible了;如果header instruction 发生了异常,pipleine需要flush, 在该exception instruc…

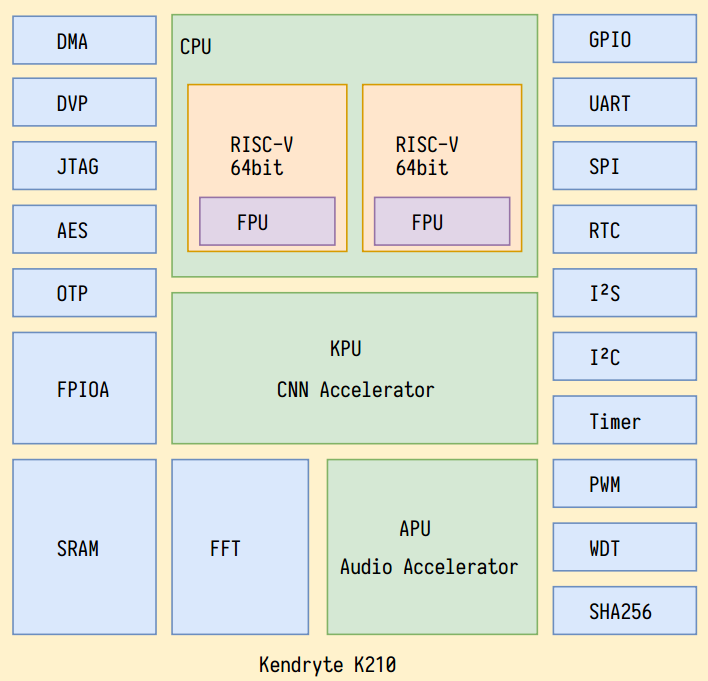

双核64位RISC-V开发板:Sipeed M1(荔枝丹),K210, ¥99.00

Sipeed M1(荔枝丹)开发板采用K210处理器,K210处理器为双核64位RV64GC,集成8MB SRAM,每个核包含32KB指令Cache和32KB数据Cache,集成卷积神经网络加速器,支持图像识别和语音识别,集成UART、IC、SPI等外设。

…

FE310三个版本的差异

FE310到目前为止(2022年2月24日)出了三个版本,分别为FE310-G000 、FE310-G002 、FE310-G003,总体上差不多,但是又有一些细节上的差异。

特性FE310-G000FE310-G002FE310-G003指令集RV32IMACRV32IMACRV32IMACI Cache16 …

RISC-V 架构寄存器规范

a0 - a7( x10 - x17 )

调用者保存,用来传递输入参数。其中的 a0 和 a1 还用来保存返回值

t0 - 6( x5 - x7, x28 - x31 )

调用者保存,作为临时寄存器使用,在被调函数中可以随意使用无需保存

s0 - s11( x8 - x9, x18…

RISC-V 编程之 Frame Pointer和 backtrace

生成的代码

一段简单的代码:

int main(void)

{blink1(10);return 0;

}未设置任何优化选项得到的编译结果,函数头部的sw s0,8(sp)和addi s0,sp,16和函数尾部的lw s0,8(sp)就是对 frame pointer 的存储和恢复。s0 寄存器即 fp 寄存器:

00000…

【RISC-V】RISC-V寄存器

一、通用寄存器

32位RISC-V体系结构提供32个32位的整型通用寄存器寄存器别名全称说明X0zero零寄存器可做源寄存器(rs)或目标寄存器(rd)X1ra链接寄存器保存函数返回地址X2sp栈指针寄存器指向栈的地址X3gp全局寄存器用于链接器松弛优化X4tp线程寄存器常用于在OS中保存指向进程控…

Milk-V Duo移植rt-thread smart

前言 (1)PLCT实验室实习生长期招聘:招聘信息链接 (2)首先,我们拿到Milk-V Duo板子之后,我个人建议先移植大核Linux。因为那个资料相对多一点,也简单很多,现象也容易观察到…

如何加快香山处理器Chisel->Verilog编译速度

graalvm installation 更换JVM。我们推荐使用GraalVM代替OpenJDK。 使用GraalVM免费版作为JVM编译香山比OpenJDK快10%-20%。 -------------------------------------------------------------------------- https://www.graalvm.org/latest/docs/getting-started/linux/ downl…

操作系统基础知识介绍之PFP调度协议(包含时间分区PFP)

一、算法思想

PFP算法是一种在RTOS中实现抢占式固定优先级调度的方法。它的基本思想是: 对于每个任务,根据其最坏情况执行时间和截止时间,计算其优先级。 在运行时,根据任务的到达时间和优先级,将任务放入一个就绪队列…

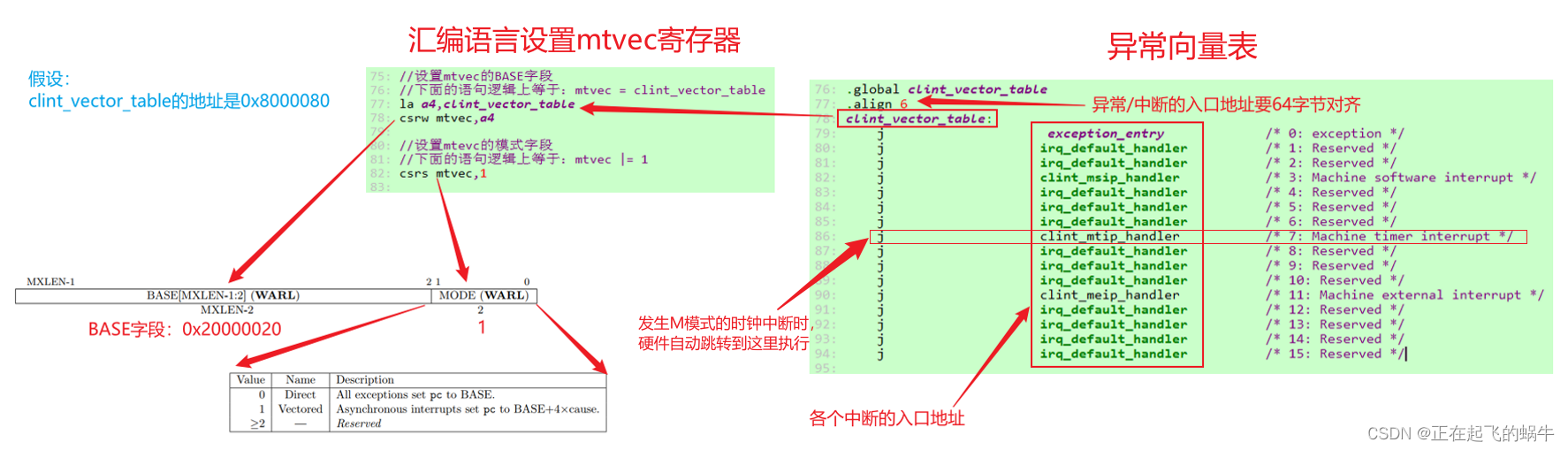

RISC-V架构——CLINT中断控制器初始化(直接模式、向量模式)

1、前言

CLINT(Core-Local Interruptor)翻译过来是核本地中断控制器,是比较简单的中断控制器,通常和PLIC(Platform-Level Interrupt COntroller)搭配使用使用CLINT涉及的MTVEC、MCAUSE寄存器,CLIC控制器也同样会使用&…

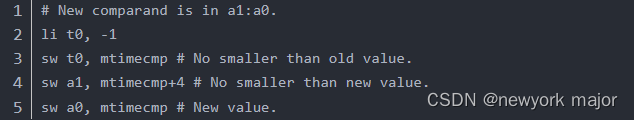

RV32I/RV32E在访问mtime和mtimecmp的注意事项

RV32I/RV32E的寄存器是32位的,而mtime和mtimecmp总是64位的,RV32I/RV32E读写mtime和mtimecmp就需要分两次Load/Store,而且mtime不停地在变化,这就需要一些技巧处理这两个寄存器的访问。

mingdu.zheng at gmail dot com http://bl…

riscv-gcc工具编译firmware进行仿真问题总结

Q1 riscv裸机编程undefined reference to _memcpy :c代码中数组长度超过16,并在定义时做初始化,编译报错问题,

Q2 全局变量初始化问题

Q3 riscv裸机编程undefined reference to _memcpy :c代码中字符数组长度超过16,并在定义时做…

【【萌新的RISC-V学习之再看计算机组成与设计大收获总六】】

萌新的RISC-V学习之再看计算机组成与设计大收获总六

我们在进行设计的时候首先要明白一点 就是 确定我们的设计所需要的 指令的大小和 地址的大小 指令集是32位的 而 地址则一般更多的是64位 数据也是64位 PC与指令寄存器之间的关系 PC是用来保存当前指令的地址。假设地址是0…

RISC-V SoC + AI | 在全志 D1「哪吒」开发板上,跑个 ncnn 神经网络推理框架的 demo

引言

D1 是全志科技首款基于 RISC-V 指令集的 SoC,主核是来自阿里平头哥的 64 位的 玄铁 C906。「哪吒」开发板 是全志在线基于全志科技 D1 芯片定制的 AIoT 开发板,是目前还比较罕见的使用 RISC-V SoC 且可运行 GNU/Linux 操作系统的可量产开发板。

n…

RISC-V公测平台发布 · 数据库在RISC-V服务器上的适配评估

前言

上一期讲到YCSB在RISC-V服务器上对MySQL进行性能测试(RISC-V公测平台发布 使用YCSB测试SG2042上的MySQL性能),在这一期文章中,我们继续深入讨论RISC-V数据库的应用。本期就继续利用HS-2平台来测试数据库软件在RISC-V服务器…

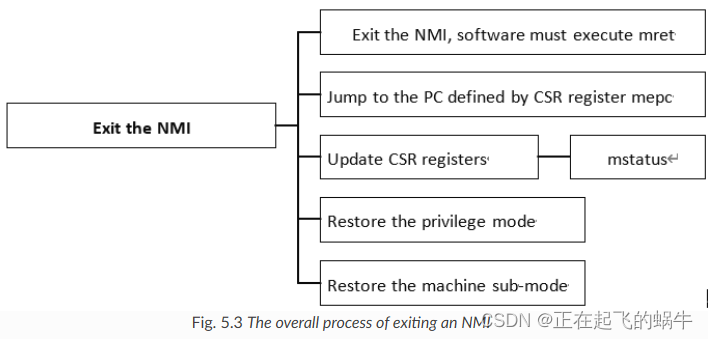

RISC-V架构的不可屏蔽中断(NMI:Non-Maskable Interrupt)介绍

1、RISC-V特权架构官方文档描述 NMI是处理器核心的一种特殊输入信号,经常用于表示系统级别的紧急错误(比如:外部硬件错误等)。在遇到NMI后,处理器应该立即中止当前程序的执行,并处理NMI错误在RISC-V架构中&…

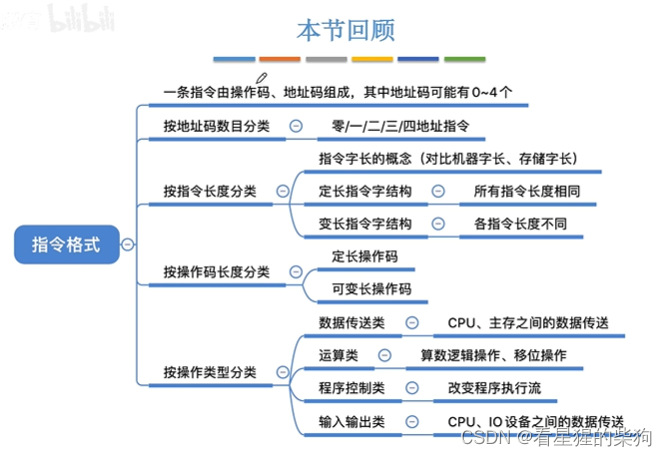

计算机组成原理-指令格式

文章目录 现代计算机的结构回忆:计算机的工作过程总览指令的定义指令格式零地址指令一地址指令二三地址指令四地址指令小结 指令-按指令长度分类指令-按操作码长度分类指令-按操作类型分类总结 现代计算机的结构 回忆:计算机的工作过程 总览 指令的定义 …

计算机体系结构基础知识介绍之缓存性能的十大进阶优化之减少命中时间和流水线访问和多组缓存增加带宽(三)

优化二:减少命中时间的方式预测

路预测是一种高速缓存优化技术,它在高速缓存中保存额外的位来预测下一次高速缓存访问的路(或者组内的块)。这种预测可以提前设置多路选择器来选择期望的块,并且在那个时钟周期内&#…

博流RISC-V芯片Eclipse环境搭建

文章目录 1、下载 Eclipse2、导入 bouffalo_sdk3、编译4、烧录5、使用ninja编译 之前编译是通过 VSCode 编译,通过手工输入 make 命令编译,我们也可以通过 Eclipse 可视化 IDE 来编译、烧录。 1、下载 Eclipse

至 Eclipse 官网 https://www.eclipse.org…

博流RISC-V芯片BL616开发环境搭建

文章目录 1、工具安装2、代码下载3、环境变量配置4、下载交叉编译器5、编译与下载运行6、使用ninja编译 本文分别介绍博流RISC-V芯片 BL616 在 Windows和Linux 下开发环境搭建,本文同时适用BL618,BL602,BL702,BL808系列芯片。 1、…

全职RISC-V芯片D1开发板使用adb串口COM连接设备和文件上传下载

将两个USB端口都连接到工作电脑

推荐使用ADB工具访问开发板,下载连接如下:

Windows版本:https://dl.google.com/android/repository/platform-tools-latest-windows.zip

Mac版本:https://dl.google.com/android/repository/pla…

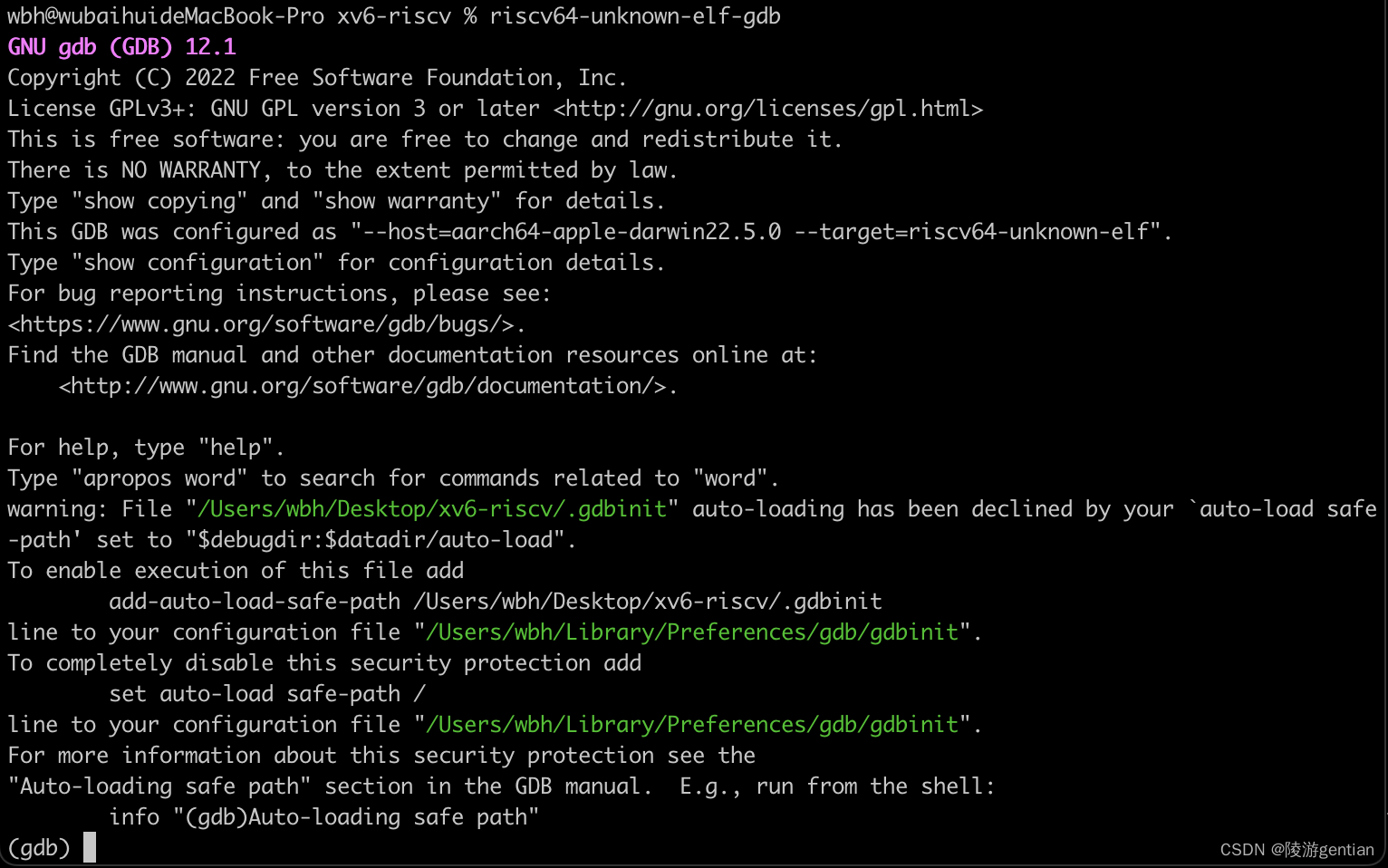

MIT 6.S081 Operating System/Fall 2020 macOS搭建risc-v与xv6开发调试环境

文章目录 本机配置安装环境Homebrew执行安装脚本查看安装是否成功 RISC-V tools执行brew的安装脚本 QEMUXV6 测试有用的参考链接(感谢前辈)写在结尾 本机配置

电脑型号:Apple M2 Pro 2023 操作系统:macOS Ventura 13.4 所以我的电…

澎峰科技|邀您关注2023 RISC-V中国峰会!

峰会概览

2023 RISC-V中国峰会(RISC-V Summit China 2023)将于8月23日至25日在北京香格里拉饭店举行。本届峰会将以“RISC-V生态共建”为主题,结合当下全球新形势,把握全球新时机,呈现RISC-V全球新观点、新趋势。

本…

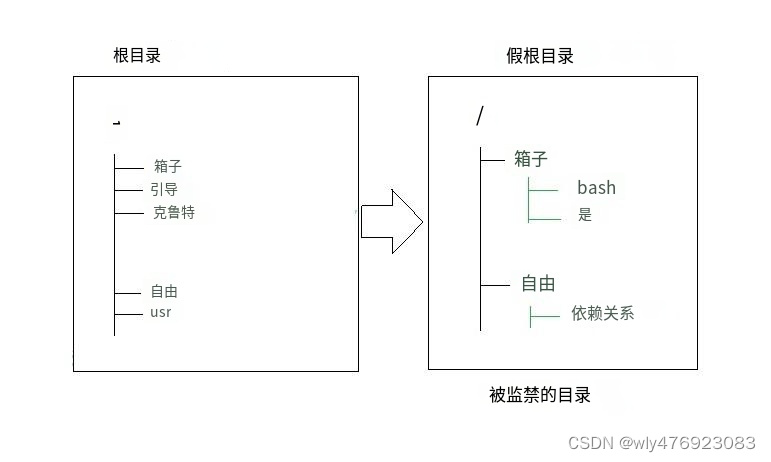

Linux 中的 chroot 命令及示例

Linux/Unix系统中的chroot命令用于更改根目录。Linux/Unix 类系统中的每个进程/命令都有一个称为root 目录的当前工作目录。它更改当前正在运行的进程及其子进程的根目录。 在此类修改的环境中运行的进程/命令无法访问根目录之外的文件。这种修改后的环境称为“ chroot监狱”或…

动能资讯 | 智慧城市:城市转型升级

随着科技的迅猛发展,智慧城市正成为城市发展的新方向和热门话题。智慧城市以其前瞻性的规划、科技的融合和可持续的发展,为人们提供更高品质的生活和工作环境,正逐渐引领着新时代的发展。

智慧城市不仅仅是城市的现代化,更是城…

从零学习开发一个RISC-V操作系统(二)丨GCC编译器和ELF格式

本篇文章的内容 一、GCC(GUN Compiler Collection)1.1 GCC的命令格式1.2 GCC的主要执行步骤1.3 GCC涉及的文件类型 二、ELF简介2.1 ELF文件格式图2.2 ELF文件处理的相关工具2.3 练习 本系列是博主参考B站课程学习开发一个RISC-V的操作系统的学习笔记&…

RISC-V数据模型,-mabi=ilp32, ilp32f, ilp32d, lp64, lp64f, lp64d

RISC-V GCC通过-mabi选项指定数据模型和浮点参数传递规则。有效的选项值包括ilp32、ilp32f、ilp32d、lp64、lp64f 和 lp64d。前半部分指定数据模型,后半部分指定浮点参数传递规则。

mingdu.zheng at gmail dot com http://blog.csdn.net/zoomdy/article/details/79…

RISC-V Reader 笔记(六)RV32V

RV32V 早期并行数据计算:采用 SIMD 单指令多数据,把一个64位宽寄存器拆成若干个32 16 8 位长度部分并行计算。这种方法前期看起来十分简单诱人。但是后来如果要扩展 SIMD 寄存器宽度,也要复杂化指令集,复杂开销越来越大。 向量操作…

【RISC-V 指令集】RISC-V DSP 扩展指令集介绍(一)

前言:

本笔记是基于对RISC-V DSP扩展指令集文档总结的,《P-ext-proposal.pdf》文档的关键内容如下: 主要介绍了RISC-V的P扩展指令集及其相关细节。

首先,对P扩展指令进行了概述,并列出了其与其他扩展重复的指令。

…

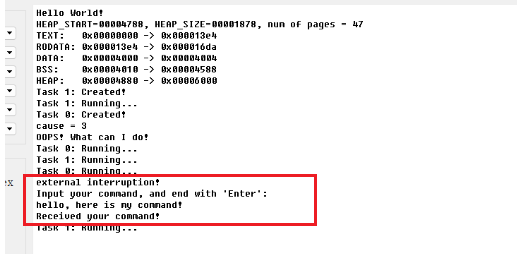

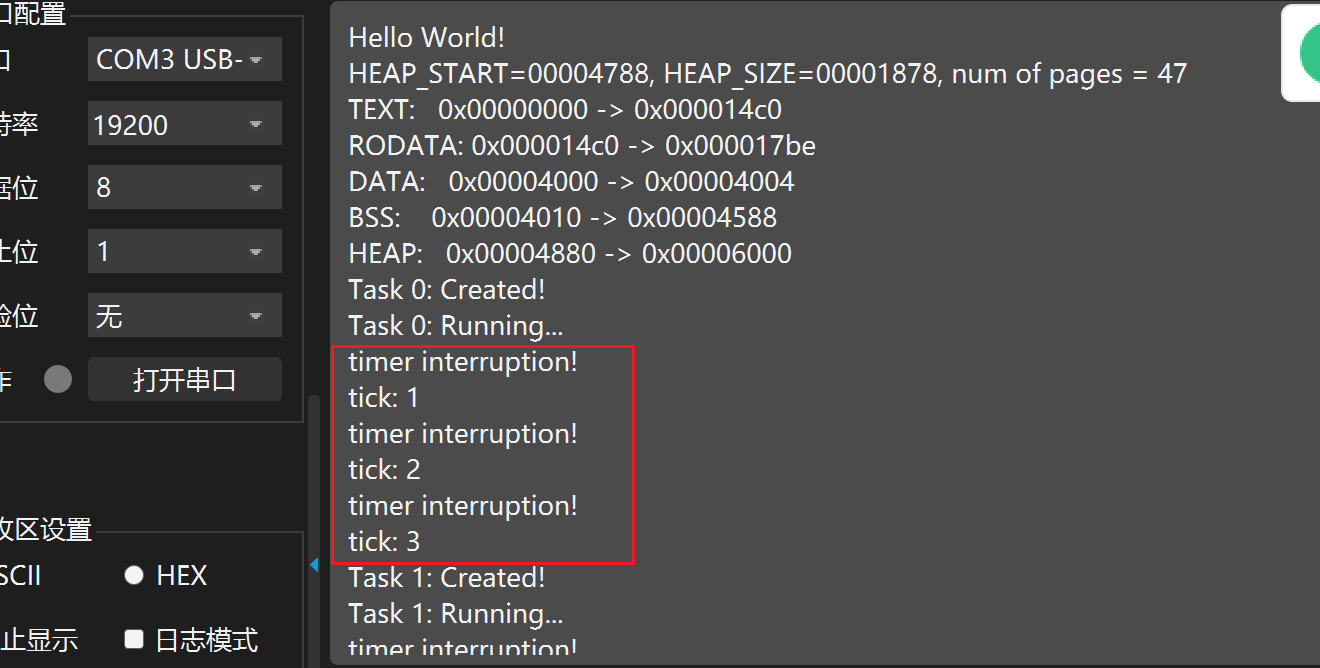

Nuclei SDK定时器应用示例

欢迎关注“安全有理”微信公众号。 概述

定时器应用demo_timer application展示了如何使用定时器中断和软件中断,实现了如下功能:

所有中断均注册为非向量中断定时器中断运行5次软件中断运行5次

中断与异常

在RISC-V体系架构中,中断处理和…

【2021集创赛】Risc-v杯一等奖:自适应噪声环境的超低功耗语音关键词识别系统

本作品参与极术社区组织的有奖征集|秀出你的集创赛作品风采,免费电子产品等你拿~活动。 团队介绍

参赛单位:东南大学 队伍名称:Hey Siri 指导老师:刘波 参赛队员:钱俊逸、张人元、王梓羽 总决赛奖项:全国一等奖

摘要…

RISC-V特权架构 - 中断与异常概述

RISC-V特权架构 - 中断与异常概述 1 中断概述2 异常概述3 广义上的异常3.1 同步异常3.2 异步异常3.3 常见同步异常和异步异常 本文属于《

RISC-V指令集基础系列教程》之一,欢迎查看其它文章。 1 中断概述 中断(Interrupt)机制,即…

使用 Ccrypt 在 Linux 中加密/解密文件

Ccrypt 是一个用于数据加密和解密的命令行工具。Ccrypt 基于 Rijndael 密码,与 AES 标准中使用的密码相同。另一方面,在 AES 标准中,使用 128 位块大小,而 ccrypt 使用 256 位块大小。Ccrypt 通常使用 .cpt 文件扩展名来表示加密文件。 它是一个轻量级的工具,该工具的安装…

HPM5300系列--第三篇 Segger Embedded Studio for RISC-V配合Jlink开发调试

一、目的 在《HPM5300系列--第一篇 命令行开发调试环境搭建》、《HPM5300系列--第二篇 Visual Studio Code开发环境以及多种调试器调试模式》我们详细介绍了HPM5300EVK开发板的开发环境以及调试方法。 本篇主要介绍Segger Embedded Studio for RISC-V配合Jlink开发调试。 二、介…

读书·计算机组成与设计:软硬件接口RISC-V版·第二章

指令:计算机的语言 指令:计算机语言的word 指令系统:计算机语言的alphabet 硬件设计三条基本原则之一:简单源于规整 汇编语言需要大量代码

java解释器采用类RV汇编方式进行解释编译,所以代码会稍多

C的代码会较少

C…

蜂鸟E203开源RISC-V开发板:蜂鸟FPGA开发板和JTAG调试器介绍

原文出处:https://mp.weixin.qq.com/s/E5X_txYlAjeixM1PsqKICg 随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》正式上市,越来越多的爱好者开始使用开源的蜂鸟E203 RISC-V处理核,很多初学者留言询问有关RISC-V工具链使…

算能RISC-V通用云编译飞桨paddlepaddle@openKylin留档

尝试一在riscv里编译飞桨。

先总结:

下载飞桨代码,参照pr修改代码

然后编译

cmake ../ -DWITH_GPUOFF -DWITH_RISCVON

make -j 16 TARGETRISCV64_GENERIC

编译好后安装:

pip install paddlepaddle-0.0.0-cp38-cp38-linux_riscv64.whl -…

fatal: unsafe repository is owned by someone else 的解决方法

在 git clone https://github.com/riscv-collab/riscv-gnu-toolchain 后执行

cd riscv-gnu-toolchain

mkdir build && cd build

../configure --prefix/opt/riscv32 --with-archrv32imc

sudo make -j8

后报错:

fatal: unsafe repository is owned by som…

DC与DCT DCG的区别

先进工艺不再wire load model进行静态时序分析,否则综合结果与后端物理电路差距很大,因此DC综合工具也进行了多次迭代,DC工具有两种模式,包括wire load mode和Topographical Mode,也就是对应的DC Expert和DC Ultra。

…

GEMM优化(RISC-V平台)

文章目录 预备知识准备工作测试交叉编译内存带宽测试roofline模型 sgemm优化使用说明Version 0: naive版本Version 1: 循环交换版本Version 2: 分块版本Version 3: 分块优化版本Version 4: B prepack版本Version 5: A pack & B prepack版本Version 6: 汇编版本Version 7: 汇…

RISC-V Linux系统rootfs制作

文章目录 1、下载2、配置与编译3、运行 buildroot 是一个构建嵌入式Linux系统的框架。整个 buildroot 是由Makefile(*.mk) 脚本和 Kconfig(Config.in) 配置文件构成的,因此可以像配置 Linux 内核一样执行 make menuconfig 进行配置,编译出一个完整的、可…

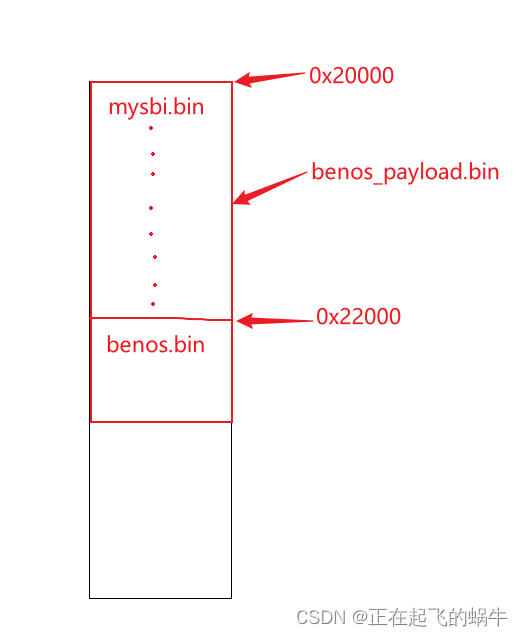

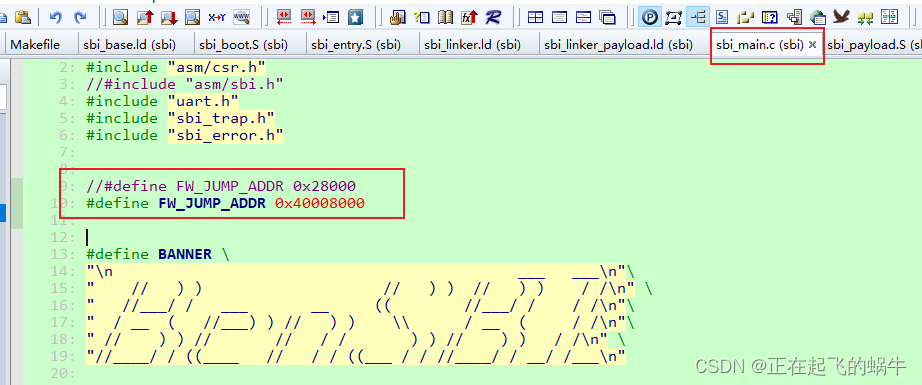

《RISC-V体系结构编程与实践》的benos_payload程序——mysbi跳转到benos分析

1、benos_payload.bin结构分析 韦东山老师提供的开发文档里已经对程序的结构做了分析,这里不再赘述,下面是讨论mysbi跳转到benos的问题; 2、mysbi跳转到benos的代码 3、跳转产生的疑问 我认为mysbi.bin最后跳转到0x22000地址处执行࿰…

2.3 opensbi: riscv: opensbi源码解析

文章目录 3. sbi_init()函数4. init_coldboot()函数4.1 sbi_scratch_init()函数4.2 sbi_domain_init()函数4.3 sbi_scratch_alloc_offset()函数4.4 sbi_hsm_init()函数4.5 sbi_platform_early_init()函数3. sbi_init()函数 函数位置:lib/sbi/sbi_init.c函数参数:scratch为每个…

RISC-V处理器设计(四)—— Verilog 代码设计

一、前言

从6月底刚开始接触 risc-v 架构,到现在完成了一个 risc-v cpu 的设计,并且成功移植了 rt-thread nano 到本 cpu 上运行,中间经过了 4个多月的时间,遇到了数不清的问题,也想过放弃,但好在最后还是…

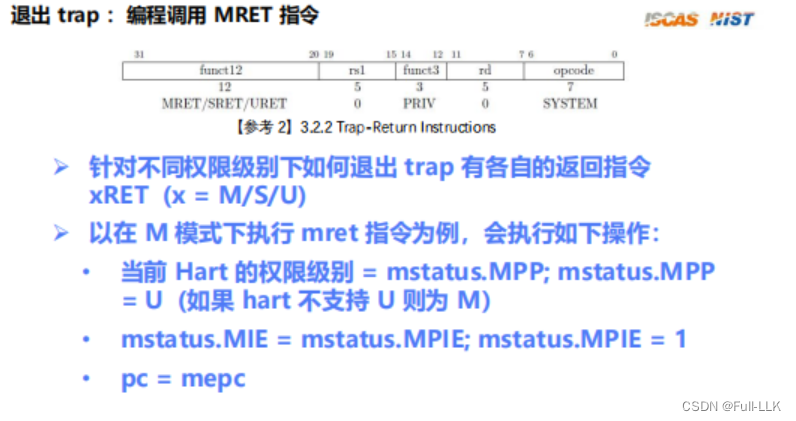

RV32/64 特权架构 - 特权模式与指令

RV32/64 特权架构 - 特权模式与指令 1 特权模式2 特权指令2.1 mret(从机器模式返回到先前的模式)2.2 sret(从监管模式返回到先前的模式)2.3 wfi(等待中断)2.4 sfence.vma(内存屏障) …

Linux 中的 comm 命令及示例

comm 逐行比较两个排序的文件并写入标准输出;常见的线条和独特的线条。

假设您有两个人员列表,并且要求您找出其中一个列表中可用而另一个列表中不可用的名称,甚至是两个列表中共有的名称。comm是帮助您实现这一目标的命令。它需要两个排序的文件,并逐行比较。在进一步讨论…

读书·基于RISC-V和FPGA的嵌入式系统设计·第二章

由于文章篇幅过大,我只会记录下自己可能会忘记的部分知识,还请见谅

-------------------------------------------------------------------------------------------

CRE-Cost 一次性工程费用 在GSDII文件格式得到采用之前,设计厂和制造厂…

risc-v编译pytorch

准备

su进入root,避免遇到权限不足情况

python3 -m venv -xxx (创建的就是一个python环境和pytorch无关,可以安装任意环境的pytorch) source进入虚拟环境

sudo apt-get install libopenblas-dev libblas-dev m4 cmake cython3 ccache 修改…

x86 ARM RISC-V 知识点

CPU架构知识点:

x86一般用于电脑,以Inter为代表,比如i9。

以计算速度快为亮点,HZ是作为计算速度的考量,i9一般是3.5G-4G HZ。

不开源 ARM用途范围特别广,除电脑外其他基本都是ARM。比如手机、电视、汽车…

芯片架构RISC-V、X86、ARM三足鼎立

2022 年 7 月,RISC-V 国际基金会首席执行官 Calista Redmond 在嵌入式世界大会上宣布 RISC-V 架构处理器核的出货数量已突破 100 亿颗。 序号架构特点代表性的厂商运营机构发明时间1X86性能高,速度快,兼容性好英特尔,AMD英特尔197…

qemu-system-riscv64 构建

qemu-system-riscv64 构建

flyfish

准备 根据自己机器实际情况进行安装

sudo apt-get install build-essential pkg-config libboost-all-dev autoconf libtool libssl-dev flex bison ninja-build libglib2.0-dev pixman-1 libpixman-1-dev libslirp-dev libncurses5-dev…

物奇5007crash问题dump、栈回溯的四种定位方法

概述

物奇属于RISC-V架构(chapter1_riscv.md 华中科技大学操作系统团队/pke-doc - Gitee.com),在遇到crash问题时,系统内部会对内存进行相关的保护和检测,当发现异常时会主动调用 IOT_ASSERT,通常会产生相关的 log 文件…

[RISCV] 为android14添加一个新的riscv device

本篇博客将基于android-14-r18添加Sifive unmatched板子的支持。

Setup build envoronment

Establishing a build environment

$ sudo apt install git-core gnupg flex bison build-essential zip curl zlib1g-dev libc6-dev-i386 libncurses5 x11proto-core-dev libx11-de…

RISC-V处理器的设计与实现(二)—— CPU框架设计

前面我们选好了要实现的指令集,并且了解了每个指令的功能(传送门:RISC-V处理器的设计与实现(一)—— 基本指令集_Patarw_Li的博客-CSDN博客),接下来我们就可以开始设计cpu了。当然我们不可能一上…

【AI简报第20230210期】 ChatGPT爆火背后、为AIoT和边缘侧AI喂算力的RISC-V

1. ChatGPT爆火背后:AI芯片迎接算力新挑战原文:https://www.163.com/dy/article/HT7BHN3C05199NPP.htmlChatGPT的出圈走红为AIGC打开全新市场增量,催生了更高的算力需求。作为人工智能三大核心要素之一,算力也被誉为人工智能“发动机”。华泰…

Windows/Ubuntu qemu虚拟机xv6-riscv利用riscv-gnu-toolchain编译安装方法

本文参考2019年版的Tools Used in 6.828(注意到当前版本也就是2020版本的Xv6, a simple Unix-like teaching operating system并没有清楚的instruction)。以下两种方法无论是使用apt安装qemu-system-misc还是编译安装qemu皆可,但不要使用apt安…

RISC-V 中国峰会 | OpenMPL引人注目,RISC-V Summit China 2023圆满落幕

RISC-V中国峰会圆满落幕 2023年8月25日,为期三天的RISC-V中国峰会(RISC-V Summit China 2023)圆满落幕。本届峰会以“RISC-V生态共建”为主题,结合当下全球新形势,把握全球新时机,呈现RISC-V全球新观点、新…

【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(一)-向量扩展编程模型

1. 引言

以下是《riscv-v-spec-1.0.pdf》文档的关键内容: 这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量…

读书·基于RISC-V和FPGA的嵌入式系统设计

引言:第八届集成电路创新创业大赛龙芯杯是有关嵌入式SoC设计的 由于我本身是做纯硬件设计,此前没怎么接触软硬协同 玩过Zynq,但是到SDK部分就去吃灰了 现在后悔了,所以,做人一定要有始有终啊~TAT

-------------------…

【学一点RISC-V】ACLINT(高级核心本地中断控制器)文档

RISCV架构 ACLINT文档 ACLINT原文档:https://github.com/riscv/riscv-aclint/blob/main/riscv-aclint.adoc 在这里进行了翻译以及校对,仅供参考,不正确的地方欢迎指出 1、介绍

【此 RISC-V ACLINT 规范定义了一组内存映射设备,这…

【RISCV】指令集

32位处理器使用的指令集简称RV32指令集 64位处理器使用的指令集简称RV64指令集

RV32I

32位基础整型指令集

RV64I

64位基础整型指令集 在RV32I基础上添加对字(word)、双子(double word)、长整型(long)版本指令的支持 所有寄存器扩展到64位

RISCV指令扩展

扩展指令集说明F单…

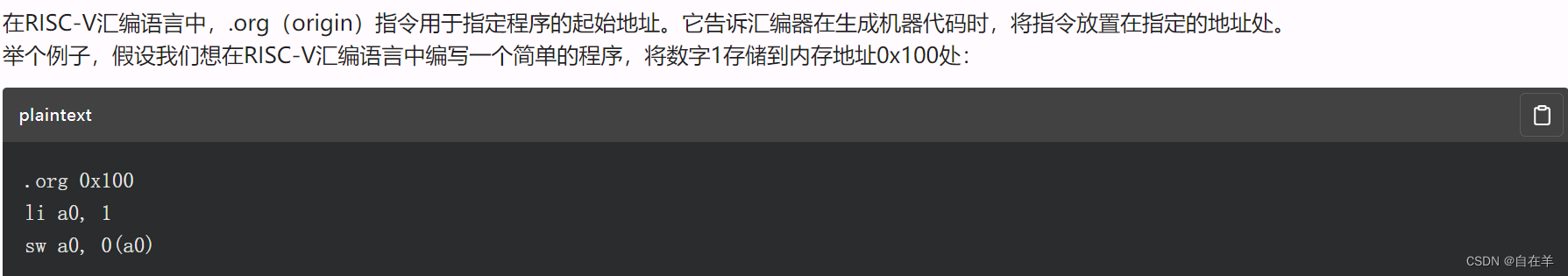

【头歌】完整汇编语言程序设计

摘自头歌实训 目录

相关知识

1.1 RISC-V 汇编语言程序基本结构

1.2 RISC-V 汇编语言程序主要元素

1.2.1 汇编指令

1.2.2 标签

1.2.3 汇编指示语句

1.3 RISC-V 汇编语言程序示例 相关知识

RISC-V 操作数类型、基本调用约定等已在前序关卡中介绍,…

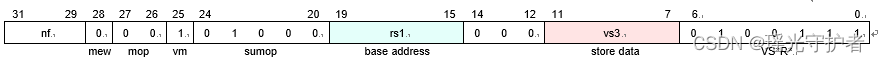

RISC-V学习基础(六)

原子指令

RV32A有两种类型的原子操作:

内存原子操作(AMO)加载保留/条件存储(load reserved/store conditional) 图6.1是RV32A扩展指令集的示意图: 图6.2列出了它们的操作码和指令格式 AMO(at…

使用 C++23 从零实现 RISC-V 模拟器(3):指令解析

指令解析

这章内容进一解析更多的指令,此外将解析指令的过程拆分为一个单独的类,采用表格驱动的方式,将数据和逻辑分离,降低了 if else 嵌套层数过多。

这部分依旧改动不多,只增加了七个指令。此外代码中细碎的变动没…

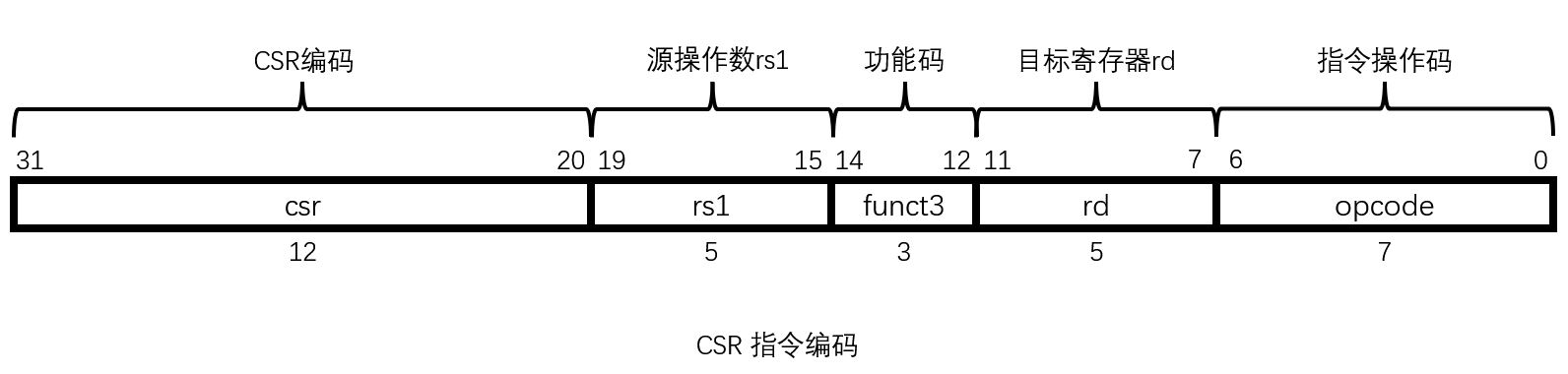

使用 C++23 从零实现 RISC-V 模拟器(5):CSR

👉🏻 文章汇总「从零实现模拟器、操作系统、数据库、编译器…」:https://okaitserrj.feishu.cn/docx/R4tCdkEbsoFGnuxbho4cgW2Yntc

RISC-V为每个hart定义了一个独立的控制状态寄存器(CSR)地址空间,提供了4…

MIT 6.S081 (BOOK-RISCV-REV1)教材第四章内容 -- 下

MIT 6.S081 教材第四章内容 -- 下 引言从内核空间陷入页面错误异常Page Fault BasicsLazy page allocationZero Fill On DemandCopy On Write ForkDemand PagingMemory Mapped Files 真实世界 引言

MIT 6.S081 2020 操作系统

本文为MIT 6.S081课程第四章教材内容翻译加整理。…

MIT 6.S081 Lab Four

MIT 6.S081 Lab Four 引言trapsRISC-V assembly (easy)代码解析 Backtrace(moderate)代码解析 Alarm(Hard)test0: invoke handler(调用处理程序)test1/test2(): resume interrupted code(恢复被中断的代码)代码解析issue解答 可选的挑战练习 引言

本文为 MIT 6.S081 2020 操作…

RISCV Reader笔记_2 RV32I

RV32I

完整的RV32I指令集可以用下面的式子中出现单词的首字母表示: 比如这一条:

set less than {immediate} {unsigned}

也就是slt slti sltu sltiu这4个指令。

RISCV指令格式如下。R 寄存器操作,I 立即数或load访存,S store访…

xv6 2020版使用gdb调试debug的方法

本文参考了MIT 6.S081 2020 操作系统 实验环境搭配详解及问题处理,作者为余晨(北海草鱼)。xv6的安装方法见Windows/Ubuntu qemu虚拟机xv6-riscv利用riscv-gnu-toolchain编译安装方法。该方法适用于Ubuntu上搭建的riscv版的xv6的QEMU虚拟机&am…

芯片功耗从28mW降到0.28mW

景芯SoC训练营培训项目,低功耗设计前,功耗为27.9mW。 低功耗设计后,功耗为0.285mW,功耗降低98.9%! (一)低功耗lowper debug

今天给大家介绍下景芯SoC训练营低功耗debug,景芯SoC在低…

RV-LINK:用RISC-V开发板做RISC-V仿真器

RV-LINK:用RISC-V开发板做RISC-V仿真器

RV-LINK v0.1 已经发布:https://gitee.com/zoomdy/RV-LINK/releases

用基于RISC-V的MCU开发板来实现RISC-V的仿真器,取名RV-LINK。(2019-09-27)用 GD32VF103C-START 和 Longan…

RISC-V嵌入式开发入门篇2:RISC-V汇编语言程序设计(中)

原文出处:https://mp.weixin.qq.com/s/3RHss3vhfK004-TtM8fpeA 随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》正式上市,越来越多的爱好者开始使用开源的蜂鸟E203 RISC-V处理核,很多初学者留言询问有关RISC-V工具链使…

RISC-V嵌入式开发入门篇2:RISC-V汇编语言程序设计(上)

原文出处:https://mp.weixin.qq.com/s/jyI-SSm_5Gg-KQyjKsIj5Q 随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》正式上市,越来越多的爱好者开始使用开源的蜂鸟E203 RISC-V处理核,很多初学者留言询问有关RISC-V工具链使…

【第三届】:“玄铁杯”RISC-V应用创新大赛(基于yolov5和OpenCv算法 — 智能警戒哨兵)

文章目录 前言

一、智能警戒哨兵是什么?

二、方案流程图

三、硬件方案

四、软件方案

五、演示视频链接

总结 前言 最近参加了第三届“玄铁杯”RISC-V应用创新大赛,我的创意题目是基于 yolov5和OpenCv算法 — 智能警戒哨兵 先介绍一下比赛…

RISC-V精简到何种程度?

RISC-V作为最新设计的精简指令集计算机体系,那么其精简到什么程度呢?

mingdu.zheng at gmail dot com http://blog.csdn.net/zoomdy/article/details/79343941

指令格式

先来看看指令格式,这格式规律地一塌糊涂啊,看着这张图&a…

RISC-V公测平台发布 · UnixBench完整测试

简介

UnixBench是一个开源的GPLv2许可的工具,它提供了对类Unix系统性能的基本指标。

通过运行UnixBench,可以获得有关系统性能的基本指标,用于与其他系统进行比较,也可以作为改进系统性能的参考。但UnixBench并不是一个综合性能…

RISC-V— 架构基础知识学习

目录 1、 概念(1)cpu(central processing unit)处理器(2)cpu Core 和 Core(3)指令集(4)指令集架构(lnstruction Set Architecture, ISA࿰…

充电保护芯片TP4054国产替代完全兼容DP4054DP4054H 锂电充电芯片

■产品概述

DP4054H是-款完整的采用恒定电流/恒定电压单节锂离子电池充电管理芯片。其SOT小封装和较少的外部元件数目使其成为便携式应用的理想器件,DP4054H可 以适合USB电源和适配器电源工作。

由于采用了内部PMOSFET架构,加上防倒充电路,所以不需要外…

HPM6750系列--第九篇 GPIO详解(基本操作)

一、目的 在之前的博文中我们主要介绍了不同系统不同开发编译调试环境的配置和操作(命令行方式、Visual Studio Code、Segger Embedded Studio for RISC-V),以帮助大家准备好学习环境为目的,但是未涉及到芯片本身以及外设的讲解。…

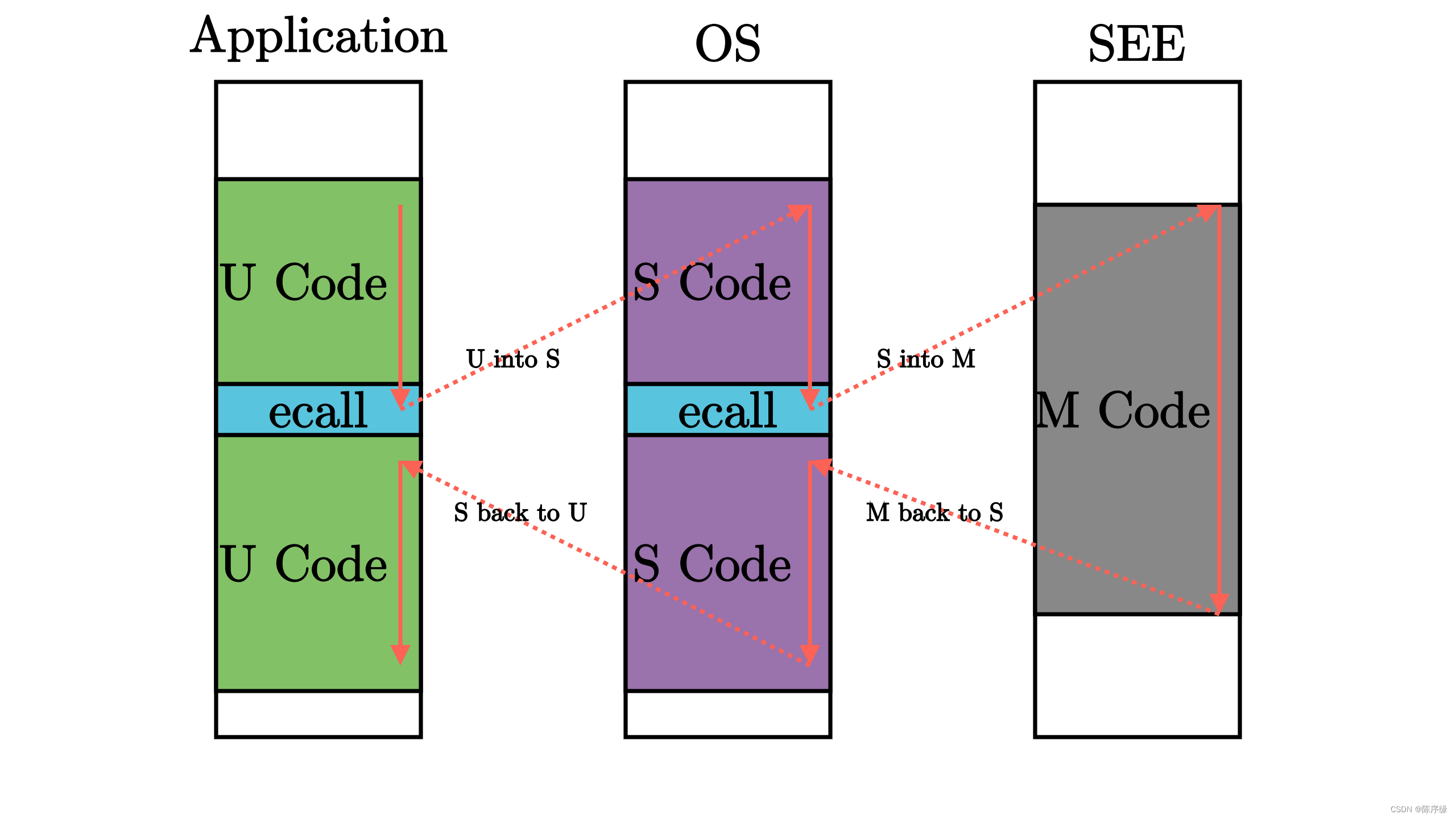

RISC-V 特权级架构

特权级别 级别的数值越大,特权级越高,掌控硬件的能力越强,在CPU硬件层面,M模式必须存在,其它模式可以不存在

执行环境调用 ecall ,这是一种很特殊的陷入类的指令, 相邻两特权级软件之间的接口正…

从CISC到RISC-V:揭开指令集的面纱

对于大多数同学来说,计算机或智能手机的运行似乎就像魔法一样神奇。你可能知道它们内部都是一些复杂的电子组件,比如CPU、内存等等,但这些组件是如何协同工作,让我们可以在电脑上打字,或者在手机上看视频呢?…

RISC-V GNU Toolchain 工具链安装问题解决(含 stdio.h 问题解决)

我的安装过程主要参照 riscv-collab/riscv-gnu-toolchain 的官方 Readme 和这位佬的博客:RSIC-V工具链介绍及其安装教程 - 风正豪 (大佬的博客写的非常详细,唯一不足就是 sudo make linux -jxx 是全部小写。) 工具链前前后后我装了…

【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(五)- 向量加载和存储

1. 引言

以下是《riscv-v-spec-1.0.pdf》文档的关键内容: 这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量…

从头开发一个RISC-V的操作系统(四)嵌入式开发介绍

文章目录 前提嵌入式开发交叉编译GDB调试,QEMU,MAKEFILE练习 目标:通过这一个系列课程的学习,开发出一个简易的在RISC-V指令集架构上运行的操作系统。 前提

这个系列的大部分文章和知识来自于:[完结] 循序渐进&#x…

【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(六)- 向量内存一致性模型

1. 引言

以下是《riscv-v-spec-1.0.pdf》文档的关键内容: 这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量…

小核引导RTOS---RISC-V C906

文章目录 参考日志编译框架目标fip 启动流程fip文件组成BL2程序 总结思考备注 参考

参考1. How does FSBL load the FreeRTOS on the small core and execute it?参考2. Duo now supports big and little cores?Come and play!Milk-V Duo, start!参考3. 使用uboo…

从头开发一个RISC-V的操作系统(五)汇编语言编程

文章目录 前提RISC-V汇编语言入门RISC-V汇编指令总览汇编指令操作对象汇编指令编码格式add指令介绍无符号数 练习参考链接 目标:通过这一个系列课程的学习,开发出一个简易的在RISC-V指令集架构上运行的操作系统。 前提

这个系列的大部分文章和知识来自于…

ARM、X86、RISC-V三分天下

引入: 简单的介绍一下X86、ARM、RISC-V三种cpu架构的区别和应用场景。 目录

简单概念讲解

1. X86架构

2. ARM架构

3. RISC-V架构

应用场景 X86、ARM和RISC-V是三种不同的CPU架构,它们在设计理念、指令集和应用场景上有一些区别。 简单概念讲解 1. X…

macOS - 上编译运行 risc-v (spike)

文章目录 一、说明二、安装步骤三、测试 一、说明

本文根据以下文章改编:

RISC-V 环境配置 https://decaf-lang.github.io/minidecaf-tutorial/docs/step0/riscv_env.html 相关链接:

riscv-gnu-toolchain GNU toolchain for RISC-V, including GCC ht…

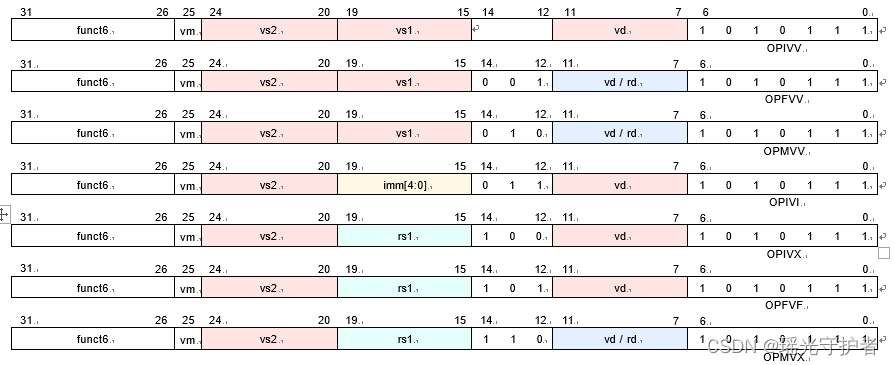

【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(七)- 向量算术指令格式

1. 引言

以下是《riscv-v-spec-1.0.pdf》文档的关键内容: 这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量…

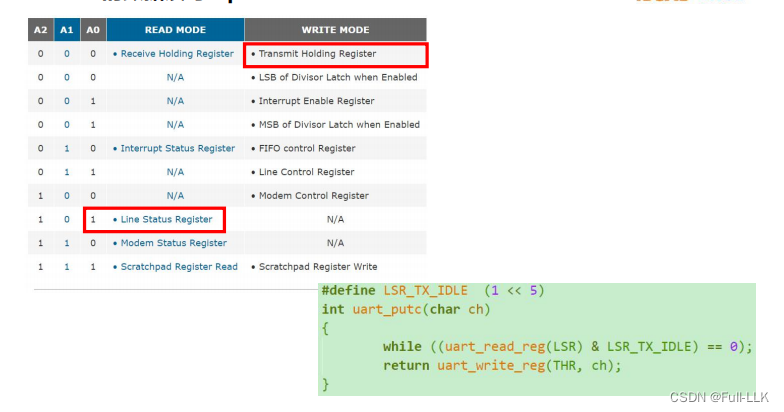

制作一个RISC-V的操作系统七-UART初始化(UART NS16550A 规定 目标 发送数据 代码 extern)

文章目录 UARTNS16550A规定目标发送数据代码extern UART

对应到嵌入式开发中,qemu模拟的就是那块开发板(硬件) 电脑使用qemu时可以理解为qemu模拟了那块板子,同时那块板子与已经与你的电脑相连接了(我们对应的指定的内…

RISC-V GNU Toolchain 工具链安装问题解决(stdio.h 问题解决,pk fence.i 问题解决)

我的安装过程主要参照 riscv-collab/riscv-gnu-toolchain 的官方 Readme 和这位佬的博客:RSIC-V工具链介绍及其安装教程 - 风正豪 (大佬的博客写的非常详细,唯一不足就是 sudo make linux -jxx 是全部小写。) 工具链前前后后我装了…

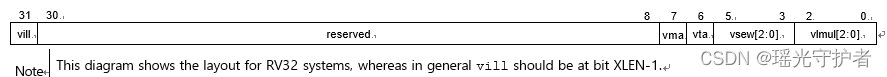

【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(四)- 配置和设置指令(vsetvli/vsetivli/vsetvl)

1. 引言

以下是《riscv-v-spec-1.0.pdf》文档的关键内容: 这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量…

制作一个RISC-V的操作系统十-Trap和Exception(流 mtvec mepc mcause mtval mstatus trap完整流程)

文章目录 流mtvecmepcmcausemtvalmstatustrap 初始化trap的top half(硬件完成)trap的bottom half(软件完成)从trap返回代码实现 流

控制流:程序控制的执行流 trap分为中断和异常

mtvec

base:存储trap入…

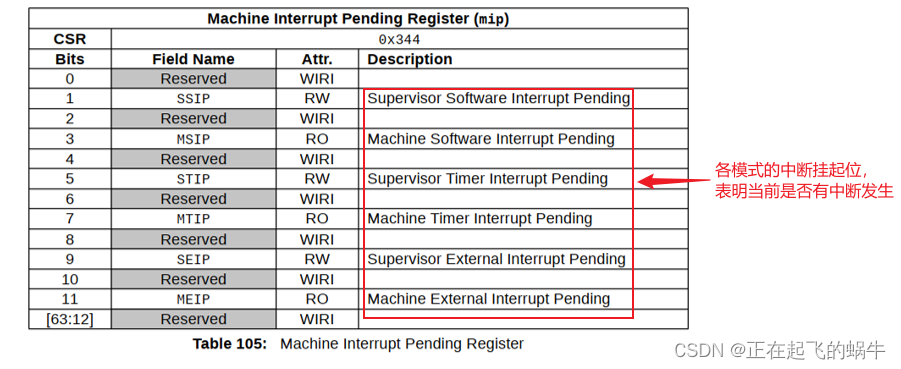

RISC-V特权架构 - 中断注入

中断注入 1 中断注入的作用2 mip寄存器3 中断注入后的处理过程 本文属于《

RISC-V指令集基础系列教程》之一,欢迎查看其它文章。 1 中断注入的作用

中断注入,就是在M模式下,手动向S模式去产生一个中断。 比如:向mip寄存器的bit5…

Nvidia H100:今年55万张够用吗?

原文标题:Nvidia H100: Are 550,000 GPUs Enough for This Year?

作者:Doug Eadline August 17, 2023

The GPU Squeeze continues to place a premium on Nvidia H100 GPUs. In a recent Financial Times article, Nvidia reports that it expects to…

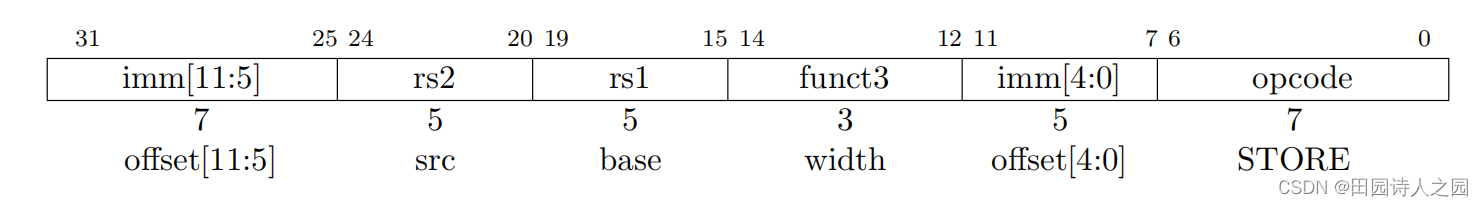

RISCV 6 RISC-V加载存储指令

RISCV 6 RISC-V加载存储指令 1 RV32I Load and Store Instructions1.1 LOAD instructions1.1.1 加载指令的指令格式1.1.2 加载指令在使用时需要注意的点 1.2 STORE instructions1.2.1 存储指令的指令格式1.2.2 存储指令在使用时需要注意的点 2 RV64 Load and Store Instruction…

【翻译】RISC-V指令集手册第Ⅱ卷:特权体系结构

第三章 机器级ISA,版本1.11

本章描述RISC-V系统中最高权限的机器模式(M-mode)下的机器级操作。M模式用于对硬件平台的低级访问,是复位时进入的第一个模式。M模式还可以用于实现在硬件中直接实现过于困难或代价过高的特性。RISC-V机器级ISA包含一个公共核…

【环境配置】基于Docker配置Chisel-Bootcamp环境

文章目录 Chisel是什么Chisel-Bootcamp是什么基于Docker配置Chisel-Bootcamp官网下载Docker安装包Docker换源启动Bootcamp镜像常用docker命令 可能产生的问题 Chisel是什么

Chisel是Scala语言的一个库,可以由Scala语言通过import引入。 Chisel编程可以生成Verilog代…

3. Linux-riscv内存管理17-20问

文章目录 2.1 请简述linux内核在理想情况下页面分配器(page allocator)是如何分区出连续物理页面的2.2 在页面分配器中,如何从分配掩码(gfp_mask)中确定可以从哪些zone中分配内存?2.3 页面分配器是按照什么方向来扫描zone的?2.4 为用户进程分配物理内存时,分配掩码应该选用…

基於RISC-V QEMU 仿真運行Linux 系統環境搭建

前言

文章詳細說明如何從堶零開始基於RISC-V QEMU 仿真運行Linux 系統環境搭建, 是Linux 小白入門教程不二之選,歡迎留言討論,轉發請注明原文出處~

1. 準備QEMU 仿真環境 --RISC-V 64bits

安裝包下載地址: https://www.qemu.org/

安裝命令及安裝成功效果如下所示,

target-…

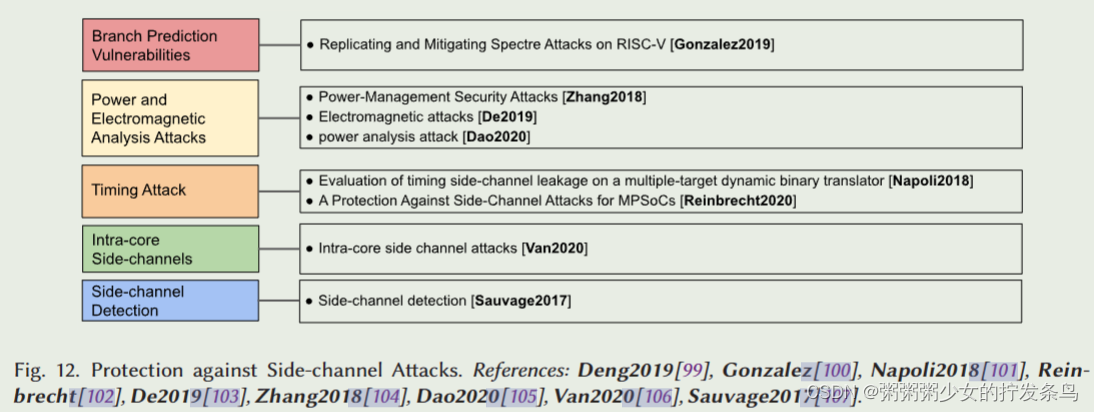

关于RISC-V安全性的全面综述

目录 摘要引言RISC-V安全综述通用平台的安全要求信任的根源与硬件安全模块OTP管理模块安全内存对称加密(如AES)引擎不对称加密[131](例如,公钥RSA)引擎HASH/HAMC引擎随机数/位生成(例如TRNG[136]࿰…

从零学习开发一个RISC-V操作系统(四)丨RISC-V汇编语言编程

本篇文章的内容 一、RISC-V汇编语言简介1.1 RISC-V 汇编语言的基本格式1.2 RISC-V 汇编指令操作对象1.3 RISC-V 汇编指令编码格式1.4 RISC-V 汇编指令分类 二、RISC-V汇编语言详解2.1 add 加法指令2.2 sub 减法指令 本系列是博主参考B站课程学习开发一个RISC-V的操作系统的学习…

沁恒CH32V307单片机入门(01):基础说明与流程体验

文章目录目的基础说明芯片介绍资料与工具开发环境流程体验开发调试下载总结目的

工作这几年单片机主要就接触过 Atmel、Renesas、Microchip、ST 这些厂家的,最近几年因为内部外部的各种因素单片机的价格和供应都挺不稳定的,将来会发生什么也不好说。另外…

「RISC-V Arch」SBI 规范解读(下)

第六章 定时器扩展(EID #0x54494D45"TIME") 这个定时器扩展取代了遗留定时器扩展(EID #0x00),并遵循 v0.2 中定义的调用规约。

6.1 函数:设置定时器(FID #0)

struct sbi…

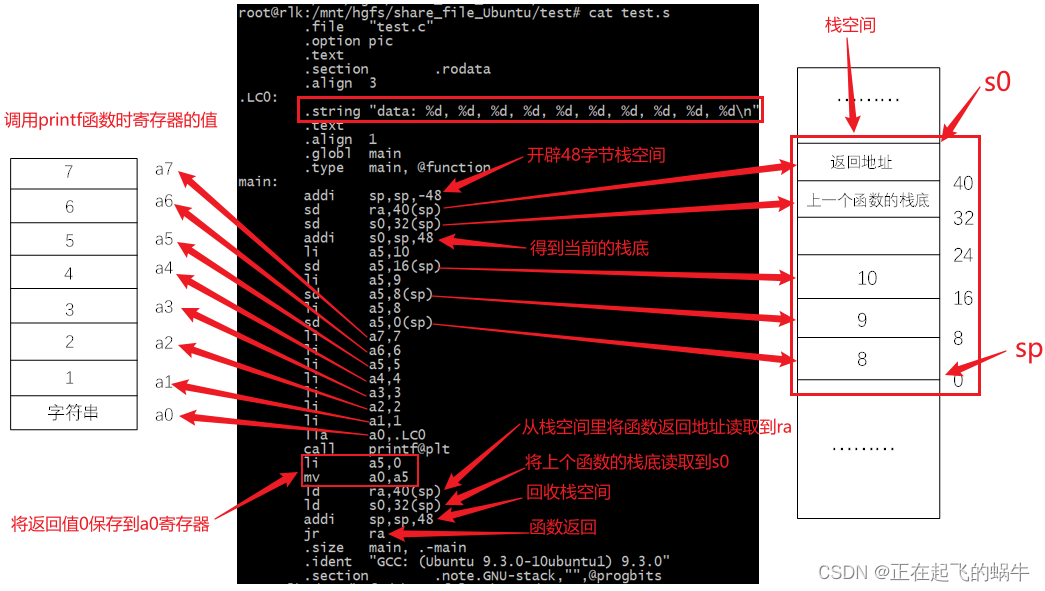

RISC-V架构的函数调用规范和栈布局

1、函数调用中寄存器规范 2、函数调用规范 (1)函数的前8个参数使用a0-a7寄存器传递,如果传参多于8个,则除前8个参数使用寄存器来传递之外,后面的参数使用栈传递; (2)如果传递的参数小…

RSIC-V工具链介绍及其安装教程

前言 (1)此系列文章是跟着汪辰老师的RISC-V课程所记录的学习笔记。 (2)该课程相关代码gitee链接; (3)PLCT实验室实习生长期招聘:招聘信息链接 (4)在配置RSIC-…

学习开发一个RISC-V上的操作系统(汪辰老师) — 环境配置

前言 (1)此系列文章是跟着汪辰老师的RISC-V课程所记录的学习笔记。 (2)该课程相关代码gitee链接; (3)PLCT实验室实习生长期招聘:招聘信息链接 (4)在学习汪辰老…

基于QEMU的RISC-V架构linux系统开发(一)——RISC-V交叉编译器的安装

基于RISC-V交叉编译器包括32bit和64bit两种类型,其中每种类型又包括裸机版本(newlib)和动态链接库版本(linux glibc)。不同类型、版本的gcc的安装仅在配置文件上存在差异,具体安装流程(以64bit …

使用VSCode调试全志R128的C906 RISC-V核心

使用 VSCode 调试

调试 XuanTie C906 核心

准备工具

T-Head DebugServer(CSkyDebugServer) - 搭建调试服务器 下载地址:T-Head DebugServer手册:T-Head Debugger Server User Guide驱动:cklink_dirvers VSCode - 开…

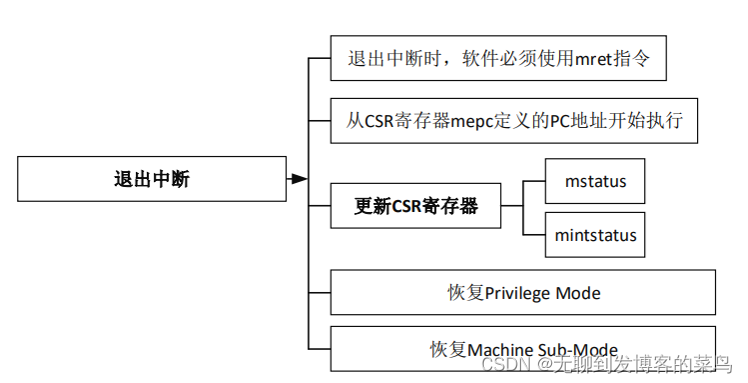

RISC-V特权架构 - 机器模式下的异常处理

RISC-V特权架构 - 机器模式下的异常处理 1 进入异常1.1 从mtvec 定义的PC 地址开始执行1.2 更新CSR 寄存器mcause1.3 更新CSR 寄存器mepc1.4 更新CSR 寄存器mtval1.5 更新CSR 寄存器mstatus 2 退出异常2.1 从mepc 定义的PC 地址开始执行2.2 更新CSR 寄存器mstatus 3 异常服务程…

RISC-V特权架构 - 特权模式与指令

RV32/64 特权架构 - 特权模式与指令 1 特权模式2 特权指令2.1 mret(从机器模式返回到先前的模式)2.2 sret(从监管模式返回到先前的模式)2.3 wfi(等待中断)2.4 sfence.vma(内存屏障) …

芯片设计—低功耗isolation cell

(一)低功耗isolation cell的目的

低功耗架构设计需要前后端拉通规划,前端设计有PMU功耗管理单元,比如A模块电压常开,B模块电压可关断,那么请思考,当B模块关断电压后,B模块输出到A模…

制作一个RISC-V的操作系统五-RISC-V汇编语言编程六(条件分支指令 伪指令 无条件跳转指令 问题 指令寻址模式总结)

文章目录 条件分支指令伪指令无条件跳转指令问题指令寻址模式总结 条件分支指令 B-type:B指代branch 6-11中:先是第11位然后才是1到4位 24-31中:先是5到10位,然后才是第12位

符号扩展,所以是-20482和20472

标号&…

AG32 MCU以太网应用实例demo

一. 前言

AGM32系列32位微控制器旨在为MCU用户提供新的自由度和丰富的兼容外设,以及兼容的引脚和功能。AG32F407系列产品具有卓越的品质,稳定性和卓越的价格价值。

AG32产品线支持其所有接口外设尽可能接近主流兼容性,并提供丰富的参考设计…

制作一个RISC-V的操作系统四-嵌入式开发介绍

文章目录 什么是嵌入式开发交叉编译查看一些GCC文件夹 调试器GDB相关语法命令 模拟器QEMUQEMU的安装和使用项目构造工具MakeMakeFile的构成make的运行 练习4-1练习4-2练习4-3 什么是嵌入式开发

程序跑到开发板上,或者说运行到硬件上 交叉编译

简单理解交叉编译来说…

分享 | 计算机组成与设计学习资料+CPU设计源码+实验报告

1.引言

百度网盘资源链接:

链接:https://pan.baidu.com/s/1Ww6u_l1L6DMXofC2HxfETw?pwdyqd6 提取码:yqd6

2.学习资源预览 2.1 包含学习手册四本:

- 计算机原理与设计:Verilog HDL版

- 计算机组成与设…

【开源鸿蒙】模拟运行OpenHarmony轻量系统QEMU RISC-V版

文章目录 一、准备工作1.1 编译输出目录简介 二、QEMU安装2.1 安装依赖2.2 获取源码2.3 编译安装2.4 问题解决 三、用QEMU运行OpenHarmony轻量系统3.1 qemu-run脚本简介3.2 qemu-run脚本参数3.3 qemu-run运行效果3.4 退出QEMU交互模式 四、问题解决五、参考链接 开源鸿蒙坚果派…

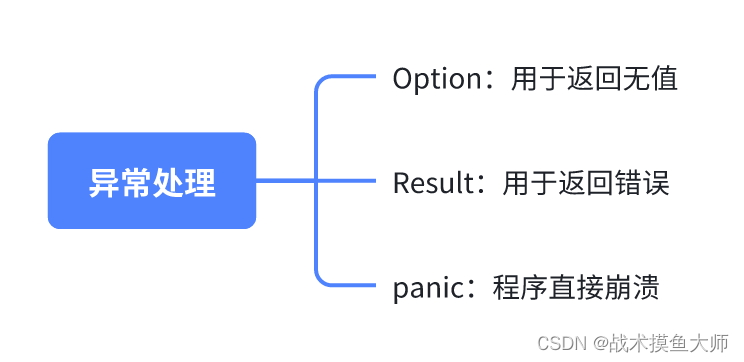

Rust编程(三)生命周期与异常处理

生命周期 生命周期,简而言之就是引用的有效作用域。在大多数时候,我们无需手动的声明生命周期,因为编译器可以自动进行推导。生命周期的主要作用是避免悬垂引用,它会导致程序引用了本不该引用的数据:

{let r;{let x …

RISC-V特权架构 - 中断定义

RISC-V特权架构 - 中断定义 1 中断类型1.1 外部中断1.2 计时器中断1.3 软件中断1.4 调试中断 2 中断屏蔽3 中断等待4 中断优先级与仲裁5 中断嵌套6 异常相关寄存器 本文属于《

RISC-V指令集基础系列教程》之一,欢迎查看其它文章。 1 中断类型

RISC-V 架构定义的中…

SUB-1G SOC芯片DP4306F 32 位 ARM Cortex-M0+内核替代CMT2380F32

DP4306F是一款高性能低功耗的单片集成收发机,集成MO核MCU,工作频率可覆盖200MHiz^ 1000MHz。 支持230/408/433/470/868/915频段。该芯片集成了射频接收器、射频发射器、频率综合器、GFSK调制器、GFSK解调器等功能模块。通过SPI接口可以对输出功率、频道选…

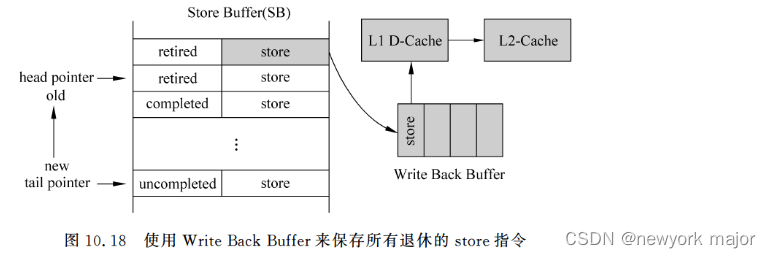

处理器中store指令的处理

对于向存储器中保存数据的store指令来说,它在顺利离开流水线之前是不允许改变处理器状态的,只有等到它退休(retire)的时候,才允许将它携带的数据写到D-Cache中在此之前,store指令即使计算完毕,也会将结果暂存在一个缓存中…

什么是RISC-V?开源 ISA 如何重塑未来的处理器设计

RISC-V代表了处理器架构的范式转变,特点是其开源模型简化了设计理念并促进了全球community-driven的开发。RISC-V导致了处理器技术发展前进方式的重大转变,提供了一个不受传统复杂性阻碍的全新视角。 RISC-V起源于加州大学伯克利分校的学术起点ÿ…

【RISC-V】如何使用release的risc-v gnu toolchain

riscv64-elf-ubuntu-22.04-gcc-nightly-2024.03.01-nightly.tar.gz 首先去release页面中获取相应的压缩包 将压缩包解压到想解压的位置,这里我选择了

mv Downloads/riscv64-elf-ubuntu-22.04-gcc-nightly-2024.03.01-nightly.tar.gz riscv64-tool-chain/然后解压…

RISC-V在快速发展的处理器生态系统中找到立足点

原文:RISC-V Finds Its Foothold in a Rapidly Evolving Processor Ecosystem

作者:Agam Shah

转载自:https://thenewstack.io/risc-v-finds-its-foothold-in-a-rapidly-evolving-processor-ecosystem/

以下是正文 But the open source pr…

在x86下运行的Ubuntu系统上部署QEMU用于模拟RISC-V硬件环境

1.配置工作环境

sudo apt install gcc bison flex libncurses-dev ninja-build \pkg-config build-essential zlib1g-dev pkg-config libglib2.0-dev \binutils-dev libboost-all-dev autoconf libtool libssl-dev \libpixman-1-dev python-capstone virtualenv software-prop…

玄铁C906——物理内存保护(PMP)介绍

1、前言 (1)本文描述的是玄铁C906的物理内存保护机制的实现中,与RISC-V架构手册中完整PMP机制的差异部分; (2)RISC-V架构的PMP机制,参考博客:《RISC-V架构——物理内存属性和物理内存…

开发一个RISC-V上的操作系统(七)—— 硬件定时器(Hardware Timer)

目录

往期文章传送门

一、硬件定时器

硬件实现

软件实现

二、上板测试 往期文章传送门 开发一个RISC-V上的操作系统(一)—— 环境搭建_riscv开发环境_Patarw_Li的博客-CSDN博客

开发一个RISC-V上的操作系统(二)—— 系统引导…

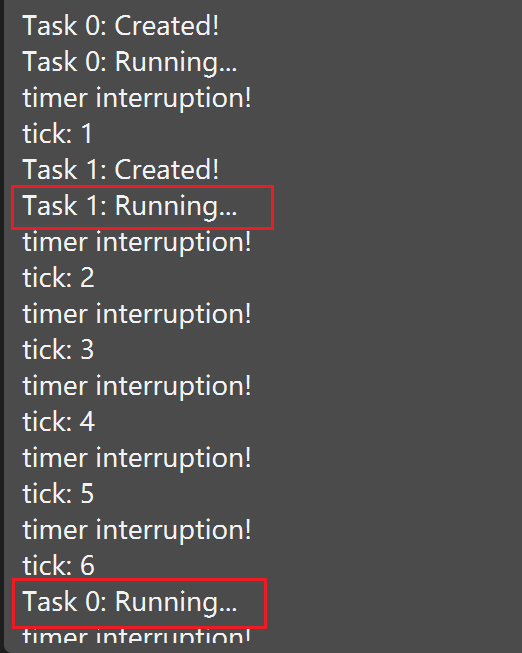

开发一个RISC-V上的操作系统(八)—— 抢占式多任务(Preemptive Multitasking)

目录

一、抢占式多任务

二、代码实现

三、上板测试 本节的代码在仓库的 06_Preemptive_Muti_Task 目录下,仓库链接:riscv_os: 一个RISC-V上的简易操作系统

本文代码的运行调试会在前面开发的RISC-V处理器上进行,仓库链接:cpu_…

Ubuntu20.04搭建RISC-V和qemu环境

1. 前言

risc-v是一个非常有潜力的指令集框架,最近对其产生了浓厚的兴趣,由于之前对于这方面的知识储备很少,在加上网上的教程都是点到为止,所以安装过程异常曲折。好在最后一步一步积累摸索,终于利用源码安装完成。看…

RISC-V处理器设计(五)—— 在 RISC-V 处理器上运行 C 程序

目录 一、前言

二、从 C 程序到机器指令

三、实验

3.1 实验环境

3.11 Windows 平台下环境搭建

3.12 Ubuntu 平台下环境搭建

3.13 实验涉及到的代码或目录

3.2 各文件作用介绍

3.2.1 link.lds

3.2.2 start.S

3.2.3 lib 和 include 目录

3.2.4 common.mk

3.2.5 demo …

Elexcon2023深圳国际电子展开幕,飞凌嵌入式重装亮相!

8月23日,Elexcon2023深圳国际电子展正式开幕,近600家全球优质品牌厂商齐聚深圳会展中心(福田),并有上万名观众来到现场参观、交流。飞凌嵌入式携多款多类型的智能主控产品及热门行业解决方案亮相盛会,展位号…

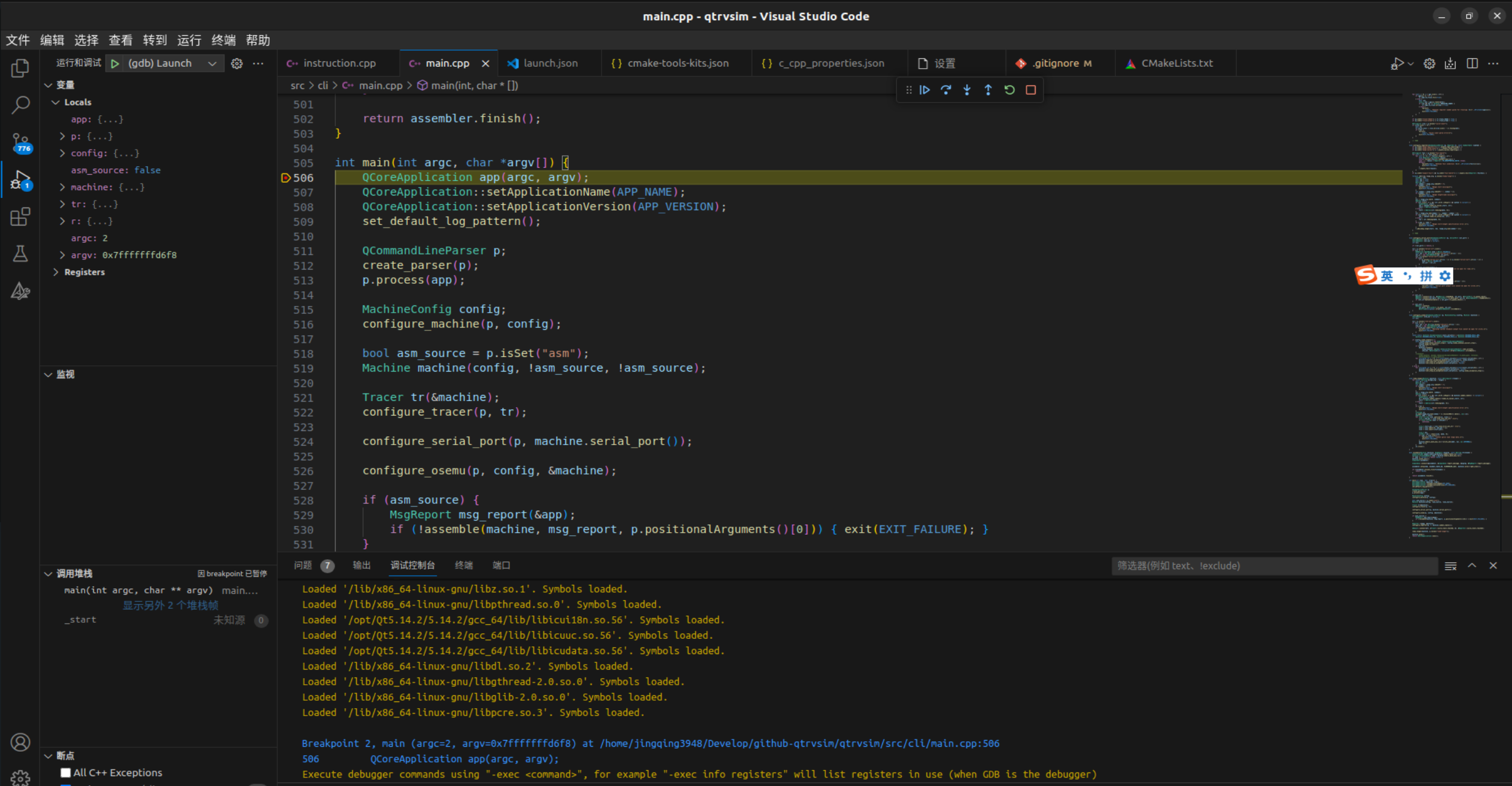

QtRVSim(二)一个 RISC-V 程序的解码流程

继上一篇文章简单代码分析后,本文主要调研如何实现对指令的解析运行。

调试配置

使用 gdb 工具跟踪调试运行。 c_cpp_properties.json 项目配置:

{"name": "QtRvSim","includePath": ["${workspaceFolder}/**&quo…

RISC-V知识总结 —— 指令集

资源1: RISC-V China – RISC-V International

资源2: RISC-V International – RISC-V: The Open Standard RISC Instruction Set Architecture

资源3: RV32I, RV64I Instructions — riscv-isa-pages documentation

1. 指令集架构的类型 在讨论RISC-V或任何处理器架构时&…

RISC-V特权架构 - CSR寄存器

RV32/64 特权架构 - CSR寄存器 1 CSR地址空间2 CSR定义2.1 用户级2.2 监管级2.3 超级监管级2.4 机器级 3 CSR访问3.1 CSRRW3.2 CSRRS3.3 CSRRC3.4 CSRRWI3.5 CSRRSI3.6 CSRRCI 本文属于《

RISC-V指令集基础系列教程》之一,欢迎查看其它文章。 1 CSR地址空间

RISC&…

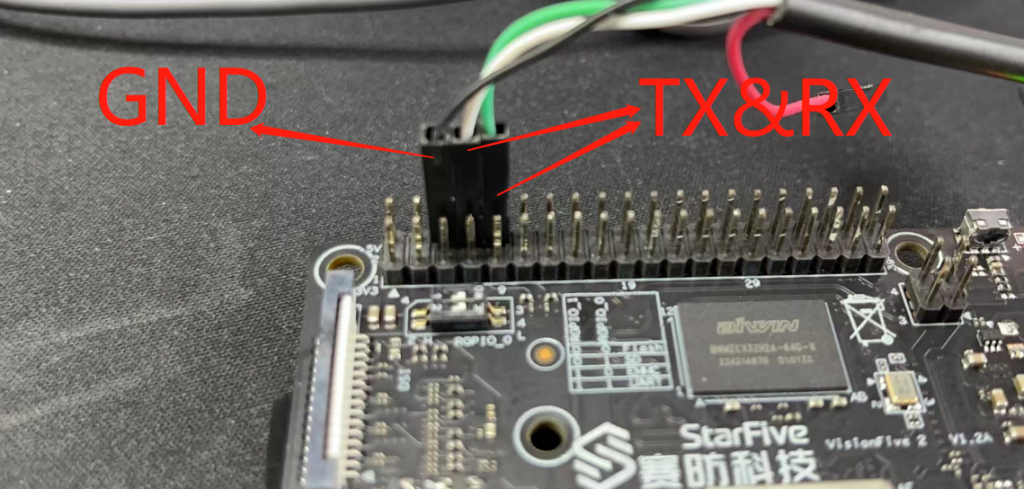

赛昉(starFive)星光2 多媒体框架分析与功能验证

开发板 开发板长这个样子: 串口调试接口如下: 整体支持情况 驱动&firmware&API jh7110/soft_3rdpart/wave511 : H.264&H.265 Decoder (Chips&Media 芯媒)jh7110/soft_3rdpart/wave521 : H.264&H.265 Encoder (Chips&Media 芯媒)jh7110/soft_3rdp…

搭建Linux内核开发环境——保姆教程(持续更新中)

搭建Linux内核开发环境——保姆教程(持续更新中) git版本管理汇编器链接器调试器编辑器构建系统模拟器文档工具图形设计工具data manage 在此文中,持续完善,搭建内核开发环境的细节,有需要的小伙伴儿可以持续关注下

g…

risc-v向量扩展strlen方法学习

riscv向量文档中给出了strlen的实现, 大概是这么一个思路,

加载向量: 使用向量加载指令(如 vload)从内存中加载一个向量长度的字符。比较向量与零: 使用向量比较指令(如 vmask 或 vcmpeq)来检查向量中的每…

【RISC-V 指令集】RISC-V 向量V扩展指令集介绍(八)- 向量整数算术指令

1. 引言

以下是《riscv-v-spec-1.0.pdf》文档的关键内容: 这是一份关于向量扩展的详细技术文档,内容覆盖了向量指令集的多个关键方面,如向量寄存器状态映射、向量指令格式、向量加载和存储操作、向量内存对齐约束、向量内存一致性模型、向量…

RISC-V特权架构 - 模式切换与委托

RISC-V特权架构 - 模式切换与委托 1 导致模式切换的常见动作2 异常处理规则3 异常处理时模式切换3.1 在U模式下,发生异常3.2 在S模式下,发生异常3.3 在M模式下,发生异常 4 系统调用时模式切换5 中断处理时模式切换 本文属于《

RISC-V指令集基…

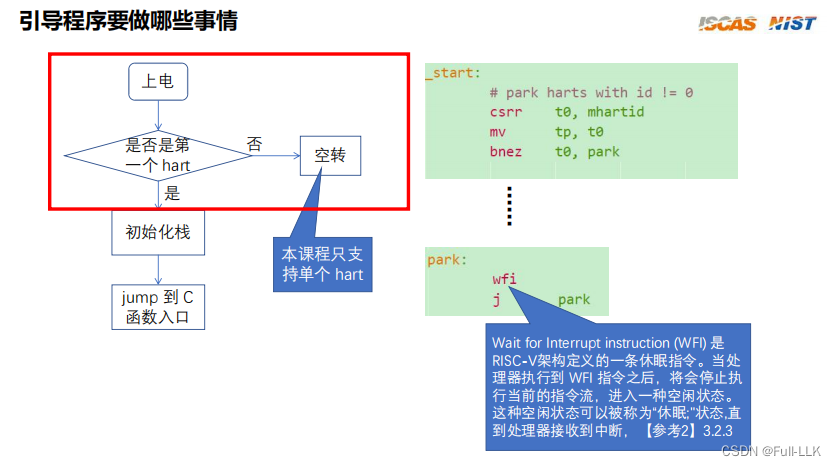

制作一个RISC-V的操作系统六-bootstrap program(risv 引导程序)

文章目录 硬件基本概念qemu-virt地址映射系统引导CSRmachine模式下的csr对应的csr指令csrrwcsrrs mhartid引导程序做的事情判断当前hart是不是第一个hart初始化栈跳转到c语言的…

![[RISC-V]verilog](https://img-blog.csdnimg.cn/419ffc5d349e4f949c65d5a0a0884d62.png)

![【PWN · ret2text | RISC-V异构】[2023 羊城杯]login](https://img-blog.csdnimg.cn/989b8062afa04f91bfa8378b366aac1d.png)

![[RISCV] 发现一个可以看RISC-V CPU行为的开源项目](https://img-blog.csdnimg.cn/direct/74eb27892818445781a2809e32f2db89.png)

![[RISC-V]Milk-V开发板 i2c测试oled及波形输出](https://img-blog.csdnimg.cn/041b873d9a2c415a99d21a57dfdbc327.png)

![[伴学笔记]01-操作系统概述 [南京大学2024操作系统]](https://img-blog.csdnimg.cn/direct/a97f807f09434d3c96625326d7deb265.png)